МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ РЯЗАНСКИЙ ГОСУДАРСТВЕННЫЙ РАДИОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

# МИКРОСХЕМОТЕХНИКА ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ

Методические указания к лабораторным работам

#### УДК 621.384.001.63; 615.47:616-072.7

Микросхемотехника цифровых интегральных схем: методические указания к лабораторным работам / Рязан. гос. радиотехн. ун-т; сост.: Н.В. Вишняков, В.В. Гудзев, А.Д. Маслов, А.С. Тюшин. Рязань, 2018. 32 с.

Содержат краткие теоретические сведения о логических элементах на основе транзисторно-транзисторной логики (ТТЛ), эмиттерно-связанной логики (ЭСЛ), интегрально-инжекционной логики ( $(^{2}\Pi)$ ), комплементарной МОП логики (КМОП), а также материалы для выполнения лабораторных работ по дисциплине «Микросхемотехника».

Предназначены для студентов дневного отделения направления 11.03.04.

Ил. 18. Библиогр.: 4 назв.

Базовые и логические элементы TTЛ, ЭСЛ,  $U^2Л$ ,  $KMO\Pi$

Печатается по решению редакционно-издательского совета Рязанского государственного радиотехнического университета.

Рецензент: кафедра микро- и наноэлектроники (зав. кафедрой д-р физ.-мат. наук, проф.Т.А. Холомина)

Микросхемотехника цифровых интрегральных схем

Составители: В и ш н я к о в Николай Владимирович

Гудзев Валерий Владимирович Маслов Алексей Дмитриевич Тюшин Андрей Сергеевич

Редактор Р.К. Мангутова Корректор С.В. Макушина

Подписано в печать 10.09.18. Формат бумаги 60×84 1/16. Бумага писчая. Печать трафаретная. Усл. печ. л. 2,0. Тираж 30 экз. Заказ

Рязанский государственный радиотехнический университет. 390005, Рязань, ул. Гагарина, 59/1. Редакционно-издательский центр РГРТУ.

#### Лабораторная работа № 1

#### Исследование характеристик элемента ТТЛ

Цель работы: изучение передаточной и переходной характеристик элемента ТТЛ и влияние на них различных факторов.

## Теоретические сведения

#### 1. Интегральные схемы транзисторно-транзисторной логики

При построении современной цифровой аппаратуры широко используют логические элементы (ЛЭ), выполненные в виде интегральных схем (ИС). Такие элементы выполняются на основе различных полупроводниковых приборов и технологий. Типичный ЛЭ состоит, как правило, из схемы, выполняющей логическую функцию, и усилителя-инвертора. В зависимости от схемотехнической и технологической реализации этих двух частей обычно и получают название логические интегральные схемы (ЛИС).

Первые ЛИС строились на основе биполярных транзисторов, а их логическая часть на основе диодов. Это обстоятельство и дало название таким схемам диодно-транзисторная логика (ДТЛ). В дальнейшем логическую часть стали выполнять на основе многоэмиттерных транзисторов (МЭТ) и появилось название транзисторно-транзисторная логика (ТТЛ). Такие ИС широко применяются в цифровой радиоэлектронной аппаратуре и в настоящее время и являются едва ли не самыми популярными в мире.

ЛИС, совместимые по конструкционно-технологическим и сигнальным параметрам, объединяют в серии, которым даются соответствующие обозначения. В разных странах и разных иностранных фирмах, производящих ЛИС, эти обозначения отличаются друг от друга. В нашей стране серии ЛИС обычно обозначаются однообразно, независимо от того, какое предприятие их производит, и различаются только присвоенными им номерами.

Базовый элемент ТТЛ представляет собой многовходовую переключательную схему, электрическое (и соответственно логическое) состояние на выходе которой определяется комбинацией входных сигналов. ТТЛ ИС обладают достаточно высоким быстродействием. Фронты сигналов ТТЛ ИС равны 2-8 нс, а задержки распространения сигнала составляют 10-30 нс. Потребляемая мощность, составляющая около 19 мВт на элемент (для одной из серий ТТЛ), является от-

носительно невысокой. ТТЛ ИС обладают сравнительно хорошей помехоустойчивостью и высокой нагрузочной способностью. Минимальная нагрузочная способность для любой серии ТТЛ ИС составляет не менее пяти единиц.

Каждая ТТЛ ИС представляет собой миниатюрный кристалл кремния площадью от 1 до  $2,5~{\rm mm}^2$  и толщиной около  $0,1~{\rm mm}$ . Кристалл помещен в корпус, имеющий гораздо большие размеры, который защищает ИС от внешних воздействий и повреждений. Для большинства ТТЛ ИС 155-й серии применяют пластмассовый прямоугольный корпус 201.14-1, имеющий  $14~{\rm выводов}$ .

ТТЛ-элементы пришли на смену элементам ДТЛ, так как многоэмиттерный транзистор ТТЛ-элемента занимал на кристалле меньшую площадь, чем диодная сборка, а также обладал меньшей паразитной ёмкостью. Затем появились ЛЭ ТТЛШ, в которых применяются *тран*зисторы Шоттки, причем в первых модификациях микросхемы ЛЭ ТТЛШ повторяли структуру элементов ТТЛ, а в последующих имели небольшие отличия

Затем появились ШТЛ ЛЭ, в которых многоэмиттерный транзистор был заменен на диодную сборку, но не на обычных диодах, а на  $\partial uo\partial ax\ \ \,$  Шотики, обладающих более высокой скоростью переключения и занимающих малую площадь. Хотя такие элементы следовало бы отнести к ДТЛ, принято причислять их к элементам ТТЛ.

## 2. Принцип действия базового элемента ТТЛ

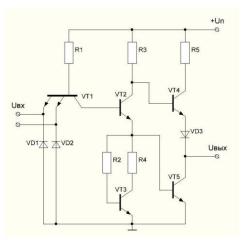

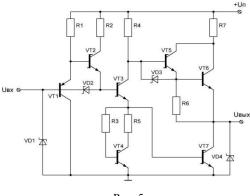

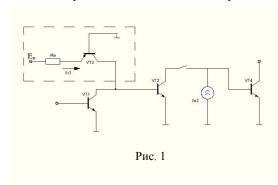

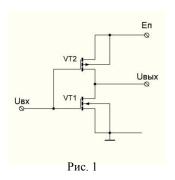

Классической структурой элемента ТТЛ является схема базового вентиля, выполняющего базисную логическую функцию «И-НЕ», серий 133 и 155. Эти ЛИС являются полными аналогами соответствующих серий SN54 и SN74 американской компании Texas Instruments. Схема (рис. 1) содержит входной каскад, реализующий функцию «И», фазоинверсный каскад с источником тока и выходной каскад с активной нагрузкой. Входной каскад построен на многоэмиттерном транзисторе VT1, созданном технологией микросборки специально для нужд логических ИС. Эмиттеры транзистора VT1 являются входами логического элемента и соединены с общей шиной через антизвонные диоды VD1 – VD2. Последние служат своего рода демпфером, защищающим VT1 от отрицательного входного напряжения. При поступлении хотя бы на один из эмиттеров потенциала, близкого к потенциалу общей шины, через эмиттерный переход, смещённый в прямом направлении, начинает вытекать весь базовый ток транзистора VT1, создавая на входе ЛЭ вытекающий *ток логического нуля*  $I_{\rm ex}^0$ . Значение этого тока ограничивается сопротивлением резистора R1. Транзистор VT1 находится в режиме насыщения, и напряжение на электродах коллектор-эмиттер невелико – порядка 0.1 - 0.15 В. В такой ситуации ток коллектора транзистора VT1 определяется током базы VT2 и пренебрежимо мал. величины недостаточно для отпирания транзистора VT2 фазоинверсного При таком распределении токов транзистор VT5 работает в режиме отсечки за

Рис. 1

счет практически нулевого падения напряжения на переходе базаэмиттер. Малая величина сопротивления резистора R5 ( $10-50~{\rm OM}$ ) приводит к тому, что VT4 выполняет роль эмиттерного повторителя, работая либо в активном режиме, либо в режиме отсечки. При запертых транзисторах VT2 и VT5 транзистор VT4 работает в активном режиме, обеспечивая на выходе уровень  $U^1_{\rm вых}$ , соответствующий напряжению логической единицы:

$$U_{BMX}^{1} = U_{II} - I_{6VT4} \cdot R3 - U_{6VT4} - U_{VD3}.$$

Если же на все эмиттеры транзистора VT1 подать напряжение  $U^1_{\,_{BX}}$ , равное примерно напряжению питания  $U_n$ , то переходы база-эмиттер транзистора VT1 сместятся в обратном направлении, а переход база-коллектор – в прямом. При этом транзистор VT1 будет работать в инверсном режиме. Токи эмиттеров этого транзистора резко сократятся (входные токи логических единиц –  $I^1_{\,_{BX}}$ ), а коллекторный ток VT1 будет втекать в базу VT2, обеспечивая его отпирание и работу в активном режиме. В таком случае транзистор VT2 фазоинверсного каскада отпирается, запирая при этом транзистор VT4 и отпирая VT5.

Включенный в коллекторную цепь транзистора VT4 диод VD3 создает необходимую при открытом до насыщения транзисторе VT5 между базой и эмиттером VT4 разность потенциалов, что обеспечивает надёжное запирание последнего. Иными словами, разность потенциалов между базой транзистора VT4 и выходом логического элемента распределяется между участком база-эмиттер транзистора VT4 и

диодом VD3. Таким образом, за счет полного запирания эмиттерного повторителя на VT4 и перехода в насыщение транзи-VT5 выходе ЛЭ формируется вень напряжепримерно ния,

равный 0,4 В. Это напряжение есть напряжение насыщения транзистора VT5 и выходное напряжение логического нуля —  $U^0_{\text{вых}}$ . Эмиттерный повторитель на транзисторе VT4 способствует улучшению *переходной динамической характеристики* логического элемента. Кроме того, каскад на транзисторе VT5, являясь активной нагрузкой транзистора VT4, улучшает *нагрузочную способность* схемы.

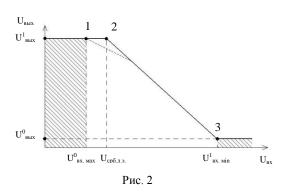

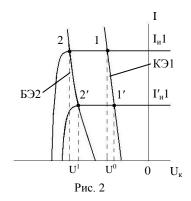

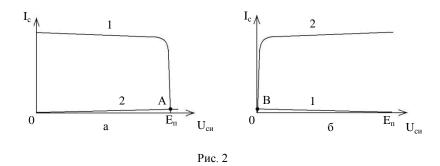

Источник тока на транзисторе VT3, резисторах R2 и R4 обеспечивает улучшение формы передаточной характеристики ЛЭ (совокупность указанных элементов также называют корректирующей иепочкой). Улучшение формы передаточной характеристики и, следовательно, помехоустойчивости устройства достигается следующим способом. При отпирании транзистора VT2 напряжение на его коллекторе начинает падать, что приводит к падению напряжения на выходе ЛЭ в соответствии с приведенной выше формулой для расчета выходного напряжения логической единицы (смотри точку 1 на рис. 2). В отсутствие источника тока, место которого может занимать резистор, в точке 1 передаточной характеристики произошел бы излом, продолжение которого показано пунктиром. Этот излом вызван протеканием тока по цепи коллектор-эмиттер транзистора VT2 при его открывании. Однако падение напряжения в эмиттерной цепи VT2, в случае использования обычного резистора вместо источника тока, ещё недостаточно для отпирания VT5 и это приводит к наличию двойного излома на передаточной характеристики такого ЛЭ. При включении в эмиттерную цепь транзистора VT2 источника тока на VT3 он проявляет свойства нелинейного сопротивления в начальный период повышения  $U_{\rm rx}$ и сильно ограничивает коллекторный ток транзистора VT2, сдерживая таким образом спад выходного напряжения  $U^{1}_{\text{вых}}$ . В то же время с повышением U<sub>вх</sub> медленно повышается потенциал эмиттера VT2 и при  $U_{\text{вx}} = U_{\text{сраб.л.9}}$  транзистор VT5 отпирается (точка 2 на рис. 2). Как видно из рис. 2, точка излома сдвинулась вправо, повысив угол наклона передаточной характеристики. Необходимо отметить, что резкого излома в точке 2 не происходит, так как ток базы VT5 повышается плавно, и в точке 2 наблюдается относительно плавный изгиб, поэтому для выявления характерных участков кривая умышленно аппроксимирована. Когда далее  $U_{\text{вх}}$  достигает значения минимально допкстимого значения выходной единицы  $U_{\text{вх. мин.}}^1 \approx 2,0$  В (точка 3 на рис. 2), переходные процессы заканчиваются, так как транзистор VT5 оказывается насыщенным и дальнейшее повышение  $U_{\text{вх}}^1$  на потенциале и токе его коллектора практически не отражается.

Отметим ещё один немаловажный момент. Переключение ЛЭ из одного устойчивого состояния в другое сопровождается переходом одного из транзисторов VT4 и VT5 в открытое состояние, а другого в закрытое. Переключение происходит синхронно, следовательно, в течение малого промежутка времени оба этих транзистора оказываются открытыми. В это время через открытые транзисторы протекает ток, значительно превышающий величину тока в статическом режиме. Указанное приводит к тому, что в динамическом режиме наблюдаются кратковременные всплески потребляемого тока, которые несколько ограничиваются резистором R5. Это является недостатком выходного каскада с активной нагрузкой и требует принятия специальных мер по защите от возникающих помех по цепям питания. Однако отмеченный недостаток компенсируется высоким быстродействием и высокой нагрузочной способностью. Повышение быстродействия связано с сокращением времени на перезаряд выходных ёмкостей.

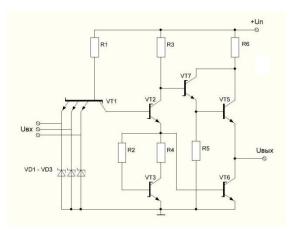

#### Особенности логических элементов серии 530, 531, SN54S, SN74S

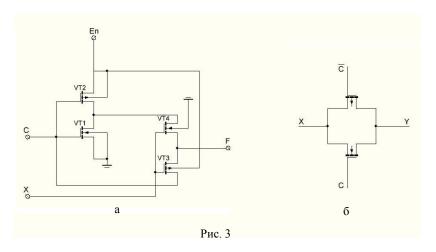

Логические элементы серий 530, 531, SN54S, SN74S явились результатом совершенствования микроэлектронной технологии, позволившей на рубеже 60-х и 70-х годов начать изготовление в масштабах серийного производства выпрямляющих контактов металлолупроводник, известных как переходы (или диоды) Шоттки. Технологии оригинально и просто решили актуальную для микросхемотехники задачу. Металлический слой интегрального п-р-п-транзистора, служащий для омического контакта с базой, был продлен в область коллектора, образовав с п-областью коллектора переход Шоттки. На схеме рис. З присутствуют такие транзисторы (их ещё называют транзисторы Шоттки), при их обозначении на принципиальных схемах

Рис. 3

базовый электрод имеет штрихи, направленные в разные стороны. Таким образом, без введения дополнительных технологических операций пебазареход коллектор оказался зашунтированным Шоттки. диодом этс обеспечило появление в схеме нелинейной отрииательной обрат-

ной связи, которая позволила в несколько раз сократить время рассасывания неосновных носителей заряда в базе транзистора при формировании положительного фронта выходного импульса. Уменьшение времени рассасывания неосновных носителей заряда позволило сократить среднее время задержки распространения сигнала в таких ЛИС.

Идея использования нелинейной отрицательной обратной связи для повышения быстродействия транзисторных ключей состоит в следующем. Известно, что время, затрачиваемое на формирование фронта выходного импульса, определяется рассасыванием неосновных инжектированных носителей, когда транзистор переходит из насыщения в область отсечки. Поэтому разумным является поиск решения, исключающего переход транзистора в глубокое насыщение. Это может быть достигнуто путем приложения к переходу база-коллектор запирающего напряжения. Если между базой и коллектором включить диод Шоттки, подключенный анодом к базе, то при отпирании транзистора на коллекторе установится потенциал, отпирающий диод Шоттки. Напряжение отпирания диода Шоттки составляет 0,4 ... 0,5 В, т.е. меньше, чем падение напряжения на переходе база-коллектор, поэтому диод Шоттки откроется раньше, чем этот переход. «Лишний» базовый ток пойдет в цепь коллектора и не будет перенасыщать базу неосновными носителями заряда. Таким образом, коллекторный переход будет смещён в обратном направлении и режим перенасыщения будет практически исключён.

Важным достоинством диодов Шоттки, помимо низкого порогового напряжения, является отсутствие *инжекции неосновных носите*-

лей заряда, в связи с чем при выключении не затрачивается время на рассасывание избыточного заряда и время переключения таких диодов составляет 0,1 нс. Если бы в качестве шунтирующего элемента был применен p-n-переход, то аналогичный результат не был бы достигнут, поскольку тогда потребовалось бы время на рассасывание неосновных носителей, но уже из p-n-перехода.

Возвращаясь к схеме ЛЭ (рис. 3), отметим, что замена антизвонных диодов на р-п-переходе на аналогичные диоды Шоттки привела к повышению быстродействия таких ИС в силу описанных свойств таких диодов. Применение в качестве выходного каскада для формирования логической единицы схемы составного эмиттерного повторителя (схемы Дарлингтона) на VT4 и VT5 приводит к повышению нагрузочной способности, а также положительно сказывается на динамических характеристиках. Причем транзистор VT5 в процессе работы ИС в насыщение не входит и не требует исполнения в виде транзистора Шоттки.

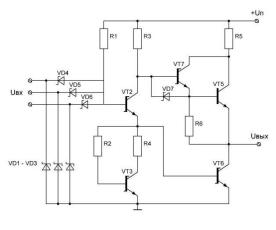

## 4. Особенности логических элементов серии 533, 555, SN54LS, SN74LS

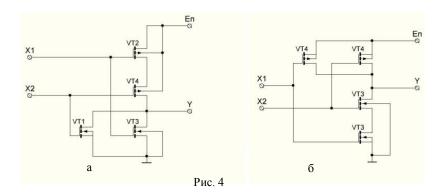

Следующим субсемейством являются ЛИС серий 533, 555, SN54LS, SN74LS. В этих сериях многоэмиттерный транзистор, реализующий логическую функцию «И», заменен диодным логическим элементом, состоящим из матрицы диодов Шоттки (рис. 4).

Логическая функция «И» реализуется на диодах VD1-VD3 и резисторе R1, а далее следует фазоинверсный каскад VT1 с источником тока на транзисторе VT2 и выходной двухтактный каскад VT3-VT5. Транзисторы всех каскадов, подобно ЛИС на рис. 3, содержат переходы Шоттки.

При подаче на катод одного из диодов VD1 – VD3 потенциала низкого логического уровня  $U^0_{\rm BX}$  транзистор VT1 запирается, так как напряжение  $U_{\rm 69VT1} = U^0_{\rm BX} + U_{\rm VD1,2,3} + U_{\rm 69VT5}$  оказывается недостаточно для его отпирания (здесь  $U_{\rm VD1,2,3}$  – падение напряжения на одном из диодов VD1 – VD3). Ток базы транзистора VT1 практически отсутствует, а входной ток  $I^0_{\rm BX}$  определяется в основном сопротивлением резистора R1. На коллекторе VT1 устанавливается потенциал, отпирающий транзисторы VT3 и VT4, и на выходе логического элемента устанавливается напряжение логической единицы  $(U^1_{\rm Bhx})$ .

Рис. 4

В случае если на все входы поступает сигнал логической единицы, то через диоды VD1 – VD3 начинает течь обратный ток, не превышающий 20 мкА и являющийся входным током логической единицы  $(I_{RX}^1)$ . Появившийся потенциал на базе VT1 оказывается достаточным ДЛЯ

отпирания VT1, он отпирается, и далее формируется уровень логического нуля  $(U^0_{\text{вых}})$  на выходе схемы.

Принцип действия каскадов на транзисторах VT2 – VT5 аналогичен работе каскадов описанных ранее серий, за небольшим исключением. Резистор R6 в этой схеме подключен уже не к общему проводу, а к коллектору транзистора VT5. Это позволяет сократить потребление тока при логической единице на выходе. Кроме того, коллектор VT1 через диод VD7 подключен к выходу схемы, что позволяет при переключении повысить коллекторный ток VT1 за счет разряда нагрузочной ёмкости этого каскада, а следовательно, увеличить быстродействие ЛИС.

По сравнению с ИС предыдущих серий, в этом субсемействе почти на порядок снижена удельная потребляемая мощность. В то же время существенное повышение экономичности привело к некоторому понижению быстродействия.

## 5. Особенности логических элементов серий 1533, SN54ALS, SN74ALS

Сериями ЛИС, в которых одинаково хорошо сочетаются экономичность и быстродействие, являются ЛИС серий 1533, SN54ALS, SN74ALS.

По сравнению субсемейством 133, 155 и другими работа переключения в них снижена в 25 раз. Столь значительное повышение показателей связано с применением улучшенной технологии создания маломощных транзисторов и диодов Шоттки ALS (Advanced Lowpower Schottky), разработанной фирмой Texas Instruments Inc. B схемо-

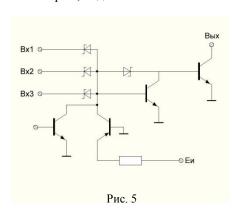

Рис. 5

техническом же плане (рис. 5) отличие заключается в применении эмиттерного повторителя VT1 на входе. Это привело к двукратному снижению входного тока  $I^0_{\rm BX}$  по сравнению с ЛИС серий 533, 555 и др. Диод VD2 позволяет разрядить входную ёмкость транзистора VT3 через открытый выходной транзистор логического элемента, подключенного к входу. Это также вносит свой вклад в увеличение быстродействия логических элементов этой серии. Сравнительные характеристики элементов ТТЛ различных серий представлены в таблице.

| Серия | $I_{BX}^0$ | $I_{BX}^1$ | $\mathrm{U}^{0}_{_{\mathrm{BX}}}$ | $U_{BX}^{1}$ | Краз | t <sup>0,1</sup> <sub>зд.р</sub> , | t <sup>1,0</sup> зд.р, | P <sub>cp</sub> , | $U^0$ , B | f <sub>π</sub> , |

|-------|------------|------------|-----------------------------------|--------------|------|------------------------------------|------------------------|-------------------|-----------|------------------|

|       | мА         | мА         | В                                 | В            |      | нс                                 | нс                     | мВт               |           | МΓц              |

| 133   | 1,6        | 0,04       | 0,4                               | 2,4          | 10   | 15                                 | 22                     | 22                | 0,4       | 10               |

| K155  | 1,6        | 0,04       | 0,4                               | 2,4          | 10   | 15                                 | 22                     | 22                | 0,4       | 10               |

| 130   | 2,3        | 0,07       | 0,35                              | 2,4          | 10   | 10                                 | 10                     | 44                | 0,4       | 30               |

| К131  | 2,3        | 0,07       | 0,35                              | 2,4          | 10   | 10                                 | 10                     | 44                | 0,4       | 30               |

| 134   | 0,18       | 0,012      | 0,3                               | 2,3          | 10   | 100                                | 100                    | 2                 | 0,35      | 3                |

| 158   | 0,15       | 0,01       | 0,3                               | 2,4          | 10   | 70                                 | 70                     | 5                 | 0,3       | 14               |

| 530   | 2          | 0,05       | 0,5                               | 2,7          | 10   | 5                                  | 4,5                    | 19                | 0,5       | 50               |

| K531  | 2          | 0,05       | 0,5                               | 2,7          | 10   | 5                                  | 4,5                    | 19                | 0,5       | 50               |

| 1531  | 1          | 0,05       | 0,5                               | 2,7          | 10   | 2,7                                | 2,7                    | 4                 | 0,5       | 60               |

| 1533  | 1          | 0,05       | 0,5                               | 2,7          | 10   | 4                                  | 4                      | 1                 | 0,5       | 15               |

| 533   | 1          | 0,05       | 0,4                               | 2,5          | 10   | 20                                 | 20                     | 3,8               | 0,5       | 10               |

| 555   | 1          | 0,05       | 0,5                               | 2,7          | 10   | 20                                 | 20                     | 3,7               | 0,5       | 10               |

#### Подготовка к работе

При подготовке к работе рекомендуется изучить теорию, представленную в методических указаниях к лабораторной работе, лекционный материал, а также дополнительную литературу.

#### Порядок выполнения работы

- 1. Получить у преподавателя вариант задания согласно номеру бригады.

- 2. Используя графический редактор программы MicroCap 9, сформировать на экране схему ТТЛ элемента с резистором вместо корректирующей цепочки.

- 3. Получить на экране графики передаточной характеристики логического элемента.

- 4. Подключить корректирующую цепочку и вновь получить передаточную характеристику ЛЭ. Сравнить эти характеристики и определить максимальную амплитуду помехи для ЛЭ с корректирующей цепочкой и без неё. Исследовать влияние изменения температуры на передаточную характеристику ЛЭ.

- 5. Получить на экране входную характеристику ЛЭ.

- 6. Получить на экране переходную характеристику ЛЭ и определить время перехода выходного напряжения из «0» в «1» и из «1» в «0», уровни напряжений логического «0» и логической «1», а также время задержки распространения сигнала.

- 7. Получить на экране эпюры переходного процесса в ЛЭ для выходного напряжения, тока базы транзистора VT2, тока базы транзистора VT4, тока коллектора VT5 и тока потребления от источника питания.

- 8. Подключить к выходу ЛЭ эквивалентную резистивноемкостную нагрузку и произвести действия по пункту 6. Сравнить полученные результаты.

## Содержание отчета

Отчет о лабораторной работе оформляется каждым студентом индивидуально и должен содержать схему ТТЛ, основные графики и параметры, полученные в ходе выполнения лабораторной работы.

## Контрольные вопросы

- 1. Рассказать общие сведения о базовом элементе ТТЛ.

- 2. Объяснить принцип работы базового элемента ТТЛ.

- 3. Рассказать об особенностях логических элементов ТТЛШ.

- 4. Рассказать об особенностях маломощных элементов ТТЛ.

## Лабораторная работа № 2

#### Исследование характеристик элемента ЭСЛ

Цель работы: изучение передаточной и переходной характеристик и измерение основных параметров элементов эмиттерносвязанной логики.

#### Теоретические сведения

#### 1. Интегральные схемы эмиттерно-связанной логики

Рассмотренные выше схемотехнические решения базовых логических элементов, предусматривающие использование биполярных транзисторов (БТ), имеют один общий принципиальный недостаток. Этот недостаток заключается в том, что переключательный транзистор в этих схемах работает в режиме насыщения. Глубокое насыщение транзистора и даже ограничение насыщения с помощью диода Шоттки, шунтирующего коллекторный переход в БТ в ТТЛ-схемах, обусловливают накопление избыточного заряда неосновных носителей в рабочих областях транзистора. Рассасывание этого избыточного заряда в основном и определяет время переходных процессов в таких схемах. Поэтому логичным представляется создание схем с ненасыщенным режимом работы переключательных транзисторов.

Одним из таких схемотехнических решений и является эмиттерно-связанная логика (ЭСЛ). Ненасыщенный режим работы транзисторов достигается применением соединенных эмиттерами транзисторных переключателей тока, работающих либо в активном режиме, либо в режиме отсечки. Рабочий ток схемы задается специальным генератором тока, включенным в эмиттерные цепи БТ. Ненасыщенный режим работы БТ позволяет увеличивать рабочие токи, необходимые для быстрой зарядки паразитных ёмкостей, и, таким образом, свести к минимуму время включения переключательного элемента без увеличения времени выключения БТ, как это имеет место в схемах насыщенного типа. Поэтому базовые элементы ЭСЛ обладают наибольшим быстродействием. Однако высокое быстродействие в таких схемах достигается путем протекания больших токов через схему, а следовательно — увеличенным энергопотреблением.

В нашей стране были выпущены несколько серий элементов ЭСЛ (К137, К187, К229, 100, К500, 500 и др.), обладающих функциональной и технической полнотой, т. е. обеспечивающих выполнение любых арифметических и логических операций, вспомогательных и специальных функций, а также хранение.

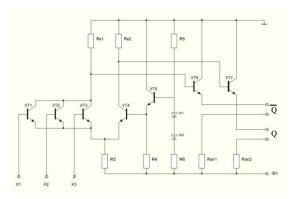

#### 2. Принцип действия базового элемента ЭСЛ

Схема базового элемента ЭСЛ представлена на рис. 1. Назначение элемента — реализация логический функции «ИЛИ», а также «ИЛИ-НЕ» в положительной логике. Уровень логической «1» ограничен пределами от -0,7 В до -0,95 В (в среднем -0,8 В), а уровень логи-

ческого «0» - пределами от -1,45 B до -1,9 B (в среднем -1,7 B).

Если хотя бы на одном из входных разъёмов X установлено напряжение -0,8 В, то на выходе Q должно установиться напряжение -0,8 В, а если на всех входах напряжение равно -1,7 В, то на выходе Q должен установиться уровень -1,7 В.

Рис. 1

Другое распространенное название элемента  ${\rm ЭСЛ}$  — «токовый переключатель», отражающее тот факт, что в схеме под действием входных сигналов ток  $I_0$  может переключаться из одной цепи в другую, вызывая требуемые изменения выходного напряжения. В элементе  ${\rm ЭСЛ}$  уровни входных сигналов выбраны по отношению к опорному напряжению ( $U_{\rm on}$  = -1,25 B, т. е.  $U_{\rm 6~VT4}$ ) такими, что если открыт транзистор VT4, то весь ток будет протекать через него, а если открыт хоть один из транзисторов VT1- VT3, то закрытым оказывается VT4 и весь ток  $I_0$  протекает через открытый (открытые) транзистор(ы). Рассмотрим такой пример. Пусть на входы X1-X3 поданы напряжения логических нулей ( $U_{\rm 61}$ = $U_{\rm 62}$ = $U_{\rm 63}$ =-1,7 B). Потенциал объединённых эмиттеров в этом случае будет равен примерно -2 В. При этом ток через транзисторы VT1- VT3 не течет, так как для их отпирания необходим такой

потенциал базы, который бы превышал потенциал эмиттера хотя бы на 0,6-0,7 В. Аналогичным образом можно показать, что если хотя бы на одном из входов, например входе X1, установлен уровень напряжения -0,8 В, а на остальных входах — уровень -1,7 В, то открыт транзистор, соответствующий этому входу, а транзисторы VT2, VT3 и, что особенно важно, VT4 закрыты. В первом случае напряжение  $U_{\text{вых. пр.}}$  = -1,7 В (0,9 В — падение напряжения на резисторе  $R_{\kappa}$  от протекания тока  $I_{\pi}$  плюс к тому 0,8 В — падение напряжения на эмиттерном переходе VT5), а напряжение на  $U_{\text{вых. инв}}$  = -0,8 В (падение напряжение  $U_{\text{вых. пр}}$  = -0,8 В, а напряжение  $U_{\text{вых. инв}}$  = -1,7 В.

Назначение эмиттерных повторителей на транзисторах VT6 и VT7:

- сдвиг уровней выходного напряжения для согласования напряжений  $U_{\text{вых}}$ ;

- обеспечение высокой нагрузочной способности ЛЭ;

- обеспечение возможности реализации функции «монтажное ИЛИ».

При реализации функции «монтажное ИЛИ» используется только один из резисторов  $R_{\rm эn}$ . Число элементов ЭСЛ, выходные сигналы которых определяются по «ИЛИ», ограничено. Так, например, для элемента К137ЛМ1, согласно справочным данным, это число равно 5.

## 3. Интегральные схемы ЭСЛ серии 500

Дальнейшее развитие схем нашло отражение в схемах 500-й серии, послужившей элементной базой ЕС ЭВМ второй очереди (ЕС-1035, ЕС-1045, ЕС-1065). Основные параметры ЭСЛ ИС серии 500 таковы:  $t_{3д}$ =1,5...2 нс, P=25 мВт (в ненагруженном состоянии), степень интеграции – до 75 ЛЭ на кристалл, логический перепад  $\Delta U_{\pi}$ =0,8 В. В функциональный набор элементов входит более 40 элементов. Следует также отметить, что расширение логических возможностей элементов осуществлено за счет применения двух- и даже трехуровневого переключения тока в токовых переключателях (ТП).

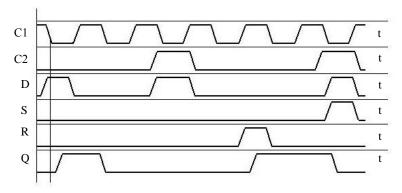

В качестве примера рассмотрим синхронный D-триггер K500TM130, в котором применено типичное двухуровневое переключение тока, схема которого приведена на рис. 2.

Рис. 2

Управление током осуществляется на двух уровнях: нижнем — ток  $I_n$  может переключаться в транзистор VT14 либо в транзистор VT15 и в верхнем — этот ток, пройдя транзистор VT14, может протекать либо через транзисторы VT6, VT7, либо через транзисторы VT8, VT9. Ток  $I_n$ , пройдя через транзистор VT15, может проходить затем либо через транзистор VT5, либо через транзистор VT10.

Транзисторы VT1, VT2 с соответствующими резисторами образуют бистабильную ячейку, в которой установление в открытое состояние одного из транзисторов приводит к запиранию другого. Транзисторы VT11 и VT17 входят в систему делителя напряжения, который обеспечивает стабильные уровни опорных напряжений, подаваемых на базы транзисторов VT10, VT15 и VT16.

Транзисторы VT12 и VT13 образуют схему «ИЛИ» для положительных синхросигналов C1 и C2. Достаточно подать высокий уровень напряжения на один из входов схемы, чтобы транзистор VT14 открылся (и обеспечил прохождение тока  $I_{\pi}$  в узел A) и закрылся транзистор VT15. Транзистор VT16 обеспечивает стабильность тока  $I_{\pi}$ .

Временные диаграммы триггера приведены на рис. 3. Как видно из этого рисунка, информация записывается в триггер (см. диаграмму Q) при подаче низких уровней напряжений на входы синхронизации

С1 и С2 и запоминается при переключении сигнала на С1 с низкого уровня на высокий. Синхросигнал С1 поступает на вход триггера постоянно, а синхросигнал С2 только тогда, когда нужно заблокировать триггер по входу D, что достигается отпиранием транзистора VT14 и запиранием транзистора VT15. При этом ток  $I_{\rm II}$  в узел B не проходит.

Рис. 3

При необходимости установки триггера в состояние «1» или «0» независимо от сигнала В высокий уровень напряжения подается на вход S или на вход R соответственно. В последнем случае транзистор VT14 должен быть заперт. Одновременно подача сигналов S и R недопустима.

#### Подготовка к работе

При подготовке к работе рекомендуется изучить теорию, представленную в методических указаниях к лабораторной работе, лекционный материал, а также дополнительную литературу.

## Порядок выполнения работы

- 1. Получить у преподавателя вариант задания согласно номеру бригады.

- 2. Используя графический редактор программы MicroCap 9, сформировать на экране схему ЛЭ на основе схемотехники ЭСЛ с резистором в цепи эмиттера.

- 3. Получить на экране передаточные характеристики ЛЭ.

- 4. Подключить вместо эмиттерного резистора генератор тока (величина тока должна быть такой же, как и в пункте 2) и вновь получить передаточную характеристику ЛЭ. Сравнить эти характеристики и оценить влияние температуры на передаточную характеристику ЛЭ.

- 5. Получить на экране входную характеристику ЛЭ.

- 6. Получить на экране переходную характеристику ЛЭ и определить время перехода выходного напряжения из «0» в «1» и из «1» в «0», уровни напряжений логического «0» и логической «1», а также время задержки распространения сигнала.

- 7. Подключить к выходу ЛЭ по указанию преподавателя эквивалентную резистивно-емкостную нагрузку и произвести действия по пункту 6. Сравнить полученные результаты.

#### Содержание отчета

Отчет о лабораторной работе оформляется каждым студентом индивидуально и должен содержать схему ЛЭ, основные графики и параметры, полученные в ходе выполнения лабораторной работы.

#### Контрольные вопросы

- 1. Рассказать общие сведения о базовом элементе ЭСЛ.

- 2. Объяснить принцип работы базового элемента ЭСЛ.

- 3. Объяснить принцип работы синхронного D-триггера на ЭСЛ элементах.

- 4. Нарисовать и объяснить временные диаграммы синхронного D-триггера.

## Лабораторная работа № 3

## Исследование характеристик элемента И<sup>2</sup>Л

Цель работы: изучение передаточной и переходной характеристик элемента и влияние на них различных факторов.

#### Теоретические сведения

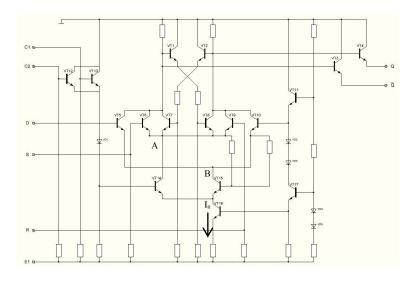

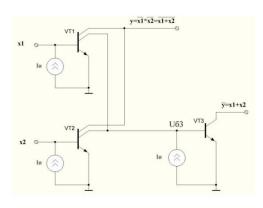

Схемы интегральной инжекционной логики ( ${\rm H}^2{\rm Л}$ ) представляют собой микросхемы на биполярных транзисторах, в которых энергия, необходимая для преобразования сигнала, обеспечивается током, подводимым специальной схемой, называемой инжектором. Для выяснения принципа действия схем с инжекционным питанием рассмотрим схему на рис. 1, которая может выполнять функцию инвертора логических переменных. Обведенная штриховой линией часть схемы на-

зывается инжектором, по структуре и принципу действия это источник тока  $I_{\rm u}1$ . Ток  $I_{\rm u}1$  в зависимости от состояния транзистора VT1 может замыкаться по одному из двух путей. Если транзистор VT1 открыт, то ток  $I_{\rm u}1$  течет в коллекторную цепь этого

транзистора, а если закрыт – в базовую цепь транзистора VT2.

На рис. 2 представлены входные ВАХ инжектора и транзистора VT1, а также ВАХ входной цепи транзистора VT2. Из графического построения видно, что точка 1 определяет значение  $U^0$ , а точка 2 — значение  $U^1$ . Таким образом, логический перепад  $\Delta U = U^1 - U^0$  составляет 0,4-0,7 В и зависит от тока  $I_3$ . Этот ток можно задавать, варьируя его значения в широких пределах от микроампер до миллиампер. Точки 1, 2 показывают, какими становятся значения  $\Delta U$ ,  $U^1$ ,  $U^0$  при токе  $I^1_{и1}$ . Транзистор VT3 формально работает в режиме насыщения  $U_{\kappa} > 0$ , но поскольку в кремниевых транзисторах

ВАХ любого перехода, в том числе и коллекторного, имеет так называемую «пятку», то достаточно сделать напряжение  $U_{\kappa}$  хотя бы на 0,1 В меньше, чем напряжение  $U_{\mathfrak{g}}$ , чтобы исключить инжекцию неосновных носителей заряда через коллекторный переход и обеспечить постоянство тока коллектора  $I_{\kappa}=I_{\mathfrak{g}}1$  и в области  $U_{\kappa}>0$ . Это условие также отражено на рис. 2.

Напряжение  $E_{\rm H}$  выбирают небольшим — в пределах 1,5 В. Изменяя  $R_{\rm H}$ , можно задавать различные токи  $I_{\rm S}$  и соответственно различные токи  $I_{\rm H}1$ .

Принцип действия логического инвертора (рис. 1) понять несложно, следует только подключить к выходу рассматриваемого элемента аналогичный элемент (транзистор VT4, инжектор  $I_{\rm H}2$ ). Если открыт транзистор VT1, то напряжение  $U_{62}$  устанавливается на уровне  $U^0$ ,

транзистор VT2 при этом закрыт, так как входная BAX транзистора имеет «пятку». Ток инжектора  $I_{\rm H}$  замыкается через коллекторную цепь насыщенного транзистора VT1.

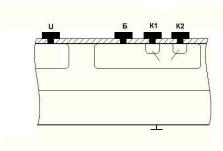

Если заперт транзистор VT1, то транзистор VT2 открыт, ток  $I_{\rm H}$  замыкается через его базовую цепь и напряжение  $U_{62}$  становится равным  $U^1$  (напряжение логической единицы). Структура и конфигурация типичной ИС с инжекционным питанием приведены на рис. 3. Области р, n, p образуют горизонтальный транзистор, входящий в схему инжектора, а n, p,  $n^+$  — вертикальный транзистор, имеющий два кол-

лектора.

Рис. 4

Площадь коллектора вертикального транзистора меньше площади эмиттера, и этот транзистор работает в инверсном включе-

нии. Такая конструкция размещается на малой площади, но при инверсном включении транзистора возникает проблема обеспечения коэффициента В, достаточного для ввода открытого транзистора в насыщение. Правда, описанная проблема не очень острая. Из рис. 3 видно, что через инжектор проходит в коллекторную цепь транзистора, например VT1, такой же ток, что и ток  $I_6$ , обеспечиваемый таким же инжектором, подключенным к базе этого транзистора, поэтому для

обеспечения насыщения транзистора VT1 необходимо и достаточно иметь B>1.

Схема «ИЛИ-НЕ» и «ИЛИ» приведена на рис. 4. Проверим, как реализуется функция  $\bar{\mathbf{y}} = \mathbf{x_1} + \mathbf{x_2}$  при условии  $\mathbf{x_1}$ =0 и  $\mathbf{x_2}$ =0. При таком сочетании сигналов транзисторы VT1 и VT2 заперты,  $\mathbf{U}_{63}$ = $\mathbf{U}^1$ , транзистор VT3 открыт и насыщен, тогда  $\bar{\mathbf{y}}$ =0. Если хотя бы на одном из входов, например на входе 1,

сигнал  $x_1$ =1, то транзистор VT1 открыт, потенциал  $U_{63}$ = $U^0$ , транзистор VT3 заперт и выходной сигнал  $\overline{y}$ =1.

Достоинством схем  $U^2\Pi$  по сравнению со схемами ТТЛ является возможность получения в 1000 раз меньшего произведения  $P \cdot t_{_{^{33}\text{CP}}}$ . Схемы  $U^2\Pi$  могут работать в широком диапазоне изменения тока  $I_{_{^{11}}}$  от микроампер до миллиампер. Для повышения быстродействия и расширения логических возможностей элементов инжекционной логики применяют диоды и транзисторы Шоттки (см. рис. 5).

Существенным недостатком схем  $И^2Л$  с непосредственными связями являются ограниченные функциональные возможности. Схемотехника инжекционной логики с непосредственными связями не позволяет реализовать комплексные логические вентили, содержащие одновременно элементы «И-НЕ» и «ИЛИ-НЕ». Поэтому с целью расширения функциональных возможностей в обычную схему элемента  $И^2Л$  между коллектором p-n-p и базой n-p-n транзистора вводят дополнительные транзисторы p-n-p-типа. Такое подключение позволяет расширить функциональные возможности формирования логических структур на инжекционных элементах.

Обычно при формировании БИС на биполярных транзисторах для уменьшения потребляемой мощности и увеличения быстродействия сложную логическую структуру БИС выполняют на элементах инжекционной логики. При вводе сигналов в микросхему используют буферные схемы, переводящие внешние логические сигналы в сигналы управления инжекционной логикой. При выводе же сигналов за пределы БИС (на внешние выводы микросхемы) применяют специальные буферные схемы, которые обеспечивают переход сигналов в стандартные логические уровни (обычно – ТТЛ) и высокую нагрузочную способность при работе таких БИС в составе электронного оборудования в радиоэлектронных системах различного типа.

## Подготовка к работе

При подготовке к работе рекомендуется изучить теорию, представленную в методических указаниях к лабораторной работе, лекционный материал, а также дополнительную литературу.

## Порядок выполнения работы

1. Получить у преподавателя вариант задания согласно номеру бригады.

- 2. Используя графический редактор программы MicroCap 9, сформировать на экране ЛЭ на основе схемотехники  $\rm H^2 J$  с идеальным генератором инжекционного тока.

- 3. Получить на экране графики передаточной характеристики ЛЭ.

- 4. Подключить вместо идеального генератора инжекционного тока генератор тока на p-n-p транзисторе (величина тока должна быть такой же, как и в пункте 2). И вновь получить передаточную характеристику ЛЭ. Сравнить эти характеристики и исследовать влияние температуры на передаточную характеристику ЛЭ.

- 5. Получить на экране переходную характеристику ЛЭ и определить время перехода выходного напряжения из <0» в <1» и из <1» в <0», уровни напряжений логического <0» и логической <1», а также время задержки распространения сигнала.

- 6. Подключить к выходу ЛЭ по указанию преподавателя эквивалентную резистивно-емкостную нагрузку и произвести действия по пункту 5. Сравнить полученные результаты.

#### Содержание отчета

Отчет о лабораторной работе оформляется каждым студентом индивидуально и должен содержать схему ЛЭ, основные графики и параметры, полученные в ходе выполнения лабораторной работы.

## Контрольные вопросы

- 1. Рассказать общие сведения о базовом элементе  $H^2\Pi$ .

- 2. Объяснить принцип работы базового элемента  $H^2\Pi$ .

- 3. Нарисовать и объяснить схемы элементов «ИЛИ-НЕ» и «ИЛИ» на  ${\rm H}^2$ Л элементах.

- 4. Достоинства и недостатки  $И^2 Л$ .

#### Лабораторная работа № 4

## Исследование характеристик логического элемента на основе КМОП-структур

Цель работы: изучение передаточной и переходной характеристик элемента и влияние на них различных факторов.

#### Теоретические сведения

## 1. Интегральные схемы на основе КМОП-структур

Первые интегральные схемы на транзисторах типа металлдиэлектрик-полупроводник появились в 1964 году. Поскольку в качестве диэлектрика в таких транзисторах применяется оксид кремния, то такие транзисторы также называют МОП-транзисторами (металокисел-полупроводник) или МОП-структурами. Схемы на таких транзисторах наиболее широко применяются в настоящее время в больших и сверхбольших интегральных схемах (БИС и СБИС соответственно). На основе таких структур создаются такие функционально законченные узлы, как постоянные и оперативные запоминающие устройства (ЗУ), электронные калькуляторы, микропроцессоры (МП) и любые другие вычислительные устройства.

В МОП интегральных схемах (ИС) можно выделить 3 направления: ИС на МОП-транзисторах р-типа, ИС на МОП-транзисторах птипа и ИС на комплементарных МОП-транзисторах (КМОП). Значение первого направления в настоящее время близко к ничтожно малому; что же касается второго и третьего, то они конкурируют друг с другом, причем по мере возрастания плотности размещения и числа элементов на кристалле третье направление уверенно опережает второе.

Основные серии элементов на комплементарных транзисторах (их иногда называют элементами с дополнительной симметрией; дополняющими транзисторами, транзисторами с разным типом прово-

димости; комплементарными структурами) относятся к потенциальным элементам.

Существует несколько разновидностей элементов ИС на КМОПтранзисторах, в том числе 164, К176, К564, 764, 765. Эти серии обладают функциональной и технической полнотой, т. е. обеспечивают выполнение любых арифметических и логических операций, вспомогательных и специальных функций, а также хранение.

Цифровые интегральные схемы на КМОП-транзисторах - наиболее перспективные. Мощность потребления таких ИС в статическом режиме не превышает десятков нановатт, быстродействие – 10 МГц. Среди ИС на МОП-транзисторах ИС на КМОП-транзисторах обладают наивысшей помехоустойчивостью: 40...45 % от величины напряпитания Отпичительная особенность ИС КМОПжения на транзисторах - высокая эффективность использования источника питания. В этих логических элементах перепад выходного напряжения почти равен напряжению источника питания. Такие ИС не чувствительны к изменению напряжения питания. В элементах на КМОПтранзисторах полярности и уровни входных и выходных напряжений совпадают, что позволяет использовать непосредственные связи между элементами.

Основными логическими элементами указанных серий являются элементы «И-НЕ»; «ИЛИ-НЕ», а базовым логическим элементом, на основе которого реализованы элементы «И-НЕ»; «ИЛИ-НЕ», - инвертор (элемент, выполняющий логическую функцию «НЕ») на КМОПтранзисторах.

## 2. Инвертор на транзисторах с разным типом проводимости

На рис. 1 приведена схема инвертора, содержащая транзисторы с индуцированными каналами n- и p-типов. Характерной чертой инвертора является то, что входное напряжение управляет не только нижним (ключевым), но и верхним (нагрузочным) транзистором. Принцип действия инвертора может быть ясен при помощи рис. 2. Обычно напряжение питания микросхем выбирают из условия

$$\left|U_{\text{nop }p}\right|+\left|U_{\text{nop }n}\right|<\left|E_{\pi}\right|.$$

Уровни входных и выходных сигналов в таких схемах составляют 0 В и  $E_{\rm II}$ . При  $U_{\rm Bx}$ =0 транзистор VT1 заперт, так как его напряжение на затворе меньше порогового напряжения  $U_{\rm 3}$ </br>  $U_{\rm 10p~II}$ . Транзистор VT2, наоборот, открыт, поскольку для него выполняется условие  $(U_{\rm 3}+U_{\rm HI})$ </br>

Напряжение  $U_{\text{вых}}$  может быть для этого случая определено следующим образом. Выходная характеристика

транзистора VT2 для напряжения  $U_3=E_\pi$  представлена на рис. 2,а кривой 1, а выходная характеристика транзистора VT1 практически совпадает с осью абсцисс (прямая 2). Их пересечение дает точку A, которая практически совпадает с точкой  $E_\pi$  на оси абсцисс. Таким образом, при  $U_{\text{вх}}=0$  получаем  $U_{\text{вых}}=E_\pi$ .

Если напряжение  $U_{\text{вх}}=E_{\text{п}}$ , то верхний транзистор заперт, а нижний открыт, режим выходной цепи определяется точкой B (рис. 2, б), которая практически совпадает с точкой 0. Таким образом, при  $U_{\text{вх}}=E_{\text{п}}$  имеем  $U_{\text{вых}}=0$ .

Рассмотрение инвертора позволяет определить ряд положительных качеств КМОП-схем:

- исключительно низкое энергопотребление в любом из статических режимов;

- работоспособность в широком диапазоне изменения Еп;

- высокую помехозащищенность (около 40 % от величины  $E_n$ );

- высокую нагрузочную способность.

Оценим мощность рассеяния инвертора с помощью формулы

$$P = P_{cr} + P_{дин},$$

где составляющая  $P_{\text{ст}}$  обычно мала и ею, как правило, пренебрегают. Динамическая мощность, расходуемая во время переключения элемента, определяется как

$$P_{\text{лин}} = P_1 + P_2 ,$$

где  $P_1$  — мощность, затрачиваемая во время заряда и разряда суммарной ёмкости нагрузки, а  $P_2$  — мощность, обусловленная протеканием тока через оба транзистора во время переключения.

Рассмотрим работу инвертора от источника идеальных прямоугольных импульсов. В этом случае транзисторы мгновенно переходят из активной области в область отсечки, поэтому можно считать, что  $P_2$ =0. Для оценки мощности  $P_1$  можно воспользоваться известной формулой

$$P_1 = E_{\pi}^2 \cdot C \cdot f$$

где f – частота входного сигнала, а C – ёмкость нагрузки.

При работе инвертора от источников импульсов с длительностью фронтов, превышающей 100 нс, мощность  $P_{\text{дин}}$  инвертора, работающего от источника питания  $E_{\text{п}}$ =10 В и имеющего выходную ёмкость

С=50 пФ, возрастает за счет роста  $P_2$ . При возрастании длительности фронта входных импульсов с 0,1 мкс до 1 мкс мощность  $P_{\text{дин}}$  возрастает в 1,5 раза за счет роста  $P_2$ .

#### 3. Элементы на КМОП-транзисторах

Рассмотрим несколько схем на КМОП-транзисторах. Инвертор с трехстабильным входом, в котором дополнительно используется управление по стокам, приведен на рис. 3,а. Если C=1, то транзистор VT1 открыт и пара транзисторов VT3, VT4 может функционировать как обычный КМОП-инвертор, преобразуя сигнал X в  $\overline{X}$ . Если C=0, то транзисторы VT1, VT3, VT4 заперты, поэтому независимо от значения X выход схемы будет высокоомным, что соответствует третьему состоянию инвертора — «отключено».

Двунаправленый ключ на двух транзисторах с разным типом проводимости приведён на рис. 3,6. Назначение ключа — передача сигнала X в случае наличия разрешения на управляющей шине C (C=1). При C=1 и X=1 открыт транзистор р-типа, на выходе устанавливается Y=1, а если X=0, то открыт транзистор п-типа и Y=0. Если C=0, то оба транзистора закрыты, потенциал на выходе может быть любым, что соответствует Z-состоянию на выходе.

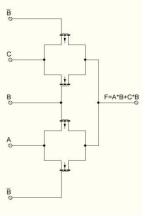

На рис 4,а приведена схема «ИЛИ-НЕ», а на рис. 4,б – схема «И-НЕ». Принцип действия этих схем становится ясным из рассмотрения различных комбинаций входных сигналов. Так, например, если в схеме «И-НЕ» на все входы подать сигнал «1», то все транзисторы п-типа будут открыты, а все транзисторы р-типа будут закрыты, получаем Y=0. Если хотя бы на один из входов подан сигнал «0», то подключенный к этому входу транзистор п-типа будет заперт, а р-типа открыт, при этом Y=1. На базе схем, показанных на рис. 3, можно реализовать ряд других логических элементов. На рис. 5 показана схема элемента, реализующего логическую функцию F=A\*B+B\*C. Отметим, что по входам А, С передаточная характеристика элемента близка к линейной:  $U_{\text{вых}} = U_{\text{вх}}$ , т. е. порог переключения отсутствует. Если на входы А и С подать взаимоинверсные сигналы, то получим элементы, реализующие функцию «исключающее ИЛИ» либо «равнозначность». Выполнение таких функций на обычных элементах КМОП требует в два раза больше транзисторов, а следовательно, и большую площадь на кристалле.

Соединяя последовательно такие элементы, можно реализовать более сложные логические функции. Однако увеличение числа последовательно включенных пар приводит к увеличению задержки из-за снижения крутизны транзисторов, что вызвано увеличением суммарной длины каналов. По этой причине число таких пар в цепи обычно не превышает 2-3, а затем включается обычный элемент КМОП, который обеспечивает необходимый порог переключения. Таким обра-

зом, логические элементы на КМОП-структурах позволяют реализовать различные по сложности логические функции при минимальном количестве транзисторов.

В настоящее время развитие технологии позволяет реализовать КМОПструктуры с очень высоким быстродействием и объединить биполярную и КМОП технологии. Такие структуры весьма успешно конкурируют с быстродействующими биполярными структурами при применении их в БИС и СБИС и называются БиКМОП-элементами (и соответственно БиКМОП технологией). Они сочетают в себе преимущества КМОП-

Рис. 5

элементов (высокую степень интеграции и малую потребляемую мощность) и ЭСЛ-микросхем (высокое быстродействие), а по входам и выходам согласуются с ТТЛ- или ЭСЛ-микросхемами.

Развитие КМОП-структур можно проследить на примере широко применяемых сегодня микросхем статических оперативных запоминающих устройств (ОЗУ). Основными тенденциями развития КМОП СБИС ОЗУ являются неуклонный рост информативной ёмкости и быстродействия, снижение удельной потребляемой мощности и стоимости, расширение номенклатуры универсальных СБИС и ОЗУ и СБИС сверхоперативных запоминающих устройств.

Рост информационной ёмкости, улучшение электрических и эксплуатационных свойств КМОП СБИС ОЗУ связаны, в первую очередь, с масштабированием размеров МОП-транзистора в микросхеме.

Минимальные геометрические размеры МОП-транзисторов ежегодно уменьшаются в 1,2 раза. Во столько же раз увеличивается площадь кристалла СБИС. Сейчас уже достигнуты почти предельные для миниатюризации проектные нормы (примерно 0,25 мкм) и толщина затвора под диэлектриком порядка единиц нанометров, в микропроцессорах широко применяются МОП-транзисторы с длиной канала, составляющей 7 нм.

Масштабирование существенно влияет на электрические параметры МОП-транзисторов и схем. При постоянном напряжении питания оно не приводит к уменьшению рассеиваемой мощности и плотности тока. По этой причине, а также для предотвращения сквозного обеднения канала при проектных нормах менее 0,7 мкм необходимо снижать напряжение питания до 3 B, при нормах в 0,25 мкм — до 1,5...2 B.

Для КМОП-инверторов в СБИС получены задержки примерно 20...30 пс при энергии переключения менее 10 фДж. Однако рост степени интеграции и быстродействия СБИС на КМОП-структурах ограничен. Это связано с приближением к физическому пределу степени интеграции, а также со сложностью и высокой стоимостью технологии их изготовления

#### Подготовка к работе

При подготовке к работе рекомендуется изучить теорию, представленную в методических указаниях к лабораторной работе, лекционный материал, а также дополнительную литературу по схемотехнике элементов на КМОП структурах.

#### Порядок выполнения работы

- 1. Получить у преподавателя вариант задания согласно номеру бригады.

- 2. Используя графический редактор программы MicroCap 9, сформировать на экране ЛЭ на основе КМОП-схемотехники.

- 3. Получить на экране графики передаточной характеристики ЛЭ.

- 4. Получить на экране переходную характеристику ЛЭ и определить время перехода выходного напряжения из «0» в «1» и из «1» в «0», уровни напряжений логического «0» и логической «1», а также время задержки распространения сигнала.

- 5. Подключить к выходу ЛЭ по указанию преподавателя эквивалентную резистивно-емкостную нагрузку и произвести действия по пункту 4. Сравнить полученные результаты.

## Содержание отчета

Отчет о лабораторной работе оформляется каждым студентом индивидуально и должен содержать схему ЛЭ, основные графики и параметры, полученные в ходе выполнения лабораторной работы.

## Контрольные вопросы

- 1. Рассказать общие сведения о базовом элементе КМОП.

- 2. Объяснить принцип работы базового элемента КМОП.

- 3. Нарисовать и объяснить схемы логических элементов на КМОП.

- 4. Рассказать о применении КМОП-элементов в современных СБИС.

## Библиографический список

- 1. Импульсно-аналоговая электроника и цифровые интегральные схемы: учеб. пособие для вузов/ А. А. Голиков, В. В. Меер; под ред. Л. Е. Смольникова. М.:МЭИ, 1983.

- 2. Алексенко А. Г., Шагурин И. И. Микросхемотехника: учеб. пособие для вузов. 2-е изд., перераб. и доп. М.: Радио и связь, 1990.

- 3. Соломатин Н. М. Логические элементы ЭВМ. М.: Высш. шк., 1987.

- 4. Новиков Ю.В. Введение в цифровую схемотехнику [Электронный ресурс] / Ю.В. Новиков. Электрон. текстовые данные. М. : Интернет-университет информационных технологий (ИНТУИТ), 2016. 392 с.

## СОДЕРЖАНИЕ

| Лабораторная работа № 1. Исследование характеристик | элемента |

|-----------------------------------------------------|----------|

| ТТЛ                                                 | 1        |

| Лабораторная работа № 2. Исследование характеристик | элемента |

| ЭСЛ                                                 | 12       |

| Лабораторная работа № 3. Исследование характеристик | элемента |

| $M^2\Pi$                                            | 18       |

| Лабораторная работа № 4. Исследование характеристи  |          |

| ского элемента на основе КМОП-структур              | 23       |

| Библиографический список                            | 31       |