#### ПРИЛОЖЕНИЕ 1

# МИНИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное бюджетное образовательное учреждение высшего образования РЯЗАНСКИЙ ГОСУДАРСТВЕННЫЙ РАДИОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ ИМЕНИ В.Ф. УТКИНА

Кафедра радиотехнических систем

## ОЦЕНОЧНЫЕ МАТЕРИАЛЫ

по дисциплине

«Проектирование средств РЭБ на ПЛИС»

Специальность – 11.05.01 «Радиоэлектронные системы и комплексы»

ОПОП специалитета «Радиоэлектронная борьба»

Квалификация выпускника – инженер Форма обучения – очная Оценочные материалы — это совокупность учебно-методических материалов (контрольных заданий, описаний форм и процедур), предназначенных для оценки качества освоения обучающимися данной дисциплины как части основной профессиональной образовательной программы.

Цель – оценить соответствие знаний, умений и уровня приобретенных компетенций, обучающихся целям и требованиям основной профессиональной образовательной программы в ходе проведения текущего контроля и промежуточной аттестации.

Основная задача — обеспечить оценку уровня сформированности общекультурных, общепрофессиональных и профессиональных компетенций, приобретаемых обучающимся в соответствии с этими требованиями.

Контроль знаний проводится в форме текущего контроля и промежуточной аттестации.

Текущий контроль успеваемости проводится с целью определения степени усвоения учебного материала, своевременного выявления и устранения недостатков в подготовке обучающихся и принятия необходимых мер по совершенствованию методики преподавания учебной дисциплины (модуля), организации работы обучающихся в ходе учебных занятий и оказания им индивидуальной помощи.

Одна из форм текущего контроля успеваемости - промежуточное тестирование обучающихся по пройденному лекционному материалу.

К контролю текущей успеваемости также относятся проверка знаний, умений и навыков, приобретенных обучающимися в ходе выполнения индивидуальных заданий на практических занятиях и лабораторных работах. При оценивании результатов освоения практических занятий и лабораторных работ применяется шкала оценки «зачтено — не зачтено». Количество лабораторных и практических работ и их тематика определена рабочей программой дисциплины, утвержденной заведующим кафедрой.

Результат выполнения каждого индивидуального задания должен соответствовать всем критериям оценки в соответствии с компетенциями, установленными для заданного раздела дисциплины.

Промежуточный контроль по дисциплине осуществляется проведением экзамена.

Форма проведения экзамена — письменный ответ по утвержденным экзаменационным билетам, сформулированным с учетом содержания учебной дисциплины. В экзаменационный билет включается два теоретических вопроса и одна задача. После выполнения письменной работы обучаемым производится ее оценка преподавателем и, при необходимости, проводится теоретическая беседа с обучаемым для уточнения экзаменационной оценки.

### Паспорт оценочных материалов по дисциплине

| №<br>п/п | Контролируемые разделы (темы) дисциплины (результаты по разделам)         | Код контролируе-<br>мой компетенции<br>(или ее части) | Вид, метод,<br>форма оценоч-<br>ного мероприя-<br>тия |

|----------|---------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| 1        | 2                                                                         | 3                                                     | 4                                                     |

| 1        | Введение. Схемотехническая реализация программируемой логики.             | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 2        | Структура проекта на языке VHDL.                                          | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 3        | Синтез комбинационных цифровых устройств на языке VHDL.                   | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 4        | Синтез последовательностных цифровых<br>устройств на языке VHDL. Часть 1. | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 5        | Синтез последовательностных цифровых устройств на языке VHDL. Часть 2.    | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 6        | Последовательные и параллельные операторы VHDL.                           | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 7        | Синтез устройств на основе счетчиков и сдвиговых регистров. Часть 1.      | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 8        | Синтез устройств на основе счетчиков и сдвиговых регистров. Часть 2.      | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 9        | Синтез цифровых фильтров для подавления радиолокационных помех.           | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 10       | Синтез цифровых конечных автоматов на языке VHDL.                         | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 11       | Синтез кодеров и декодеров помехоустойчивых кодов.                        | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 12       | Конвейерная обработка данных в ПЛИС.                                      | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 13       | Современные протоколы передачи данных и их реализация на ПЛИС.            | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

| 14       | Чтение данных с аналого-цифрового преобразователя (АЦП) AD7705.           | ПК-4.1, ПК-4.2                                        | Экзамен                                               |

Критерии оценивания уровня сформированности компетенций в процессе выполнения лабораторных работ и практических занятий:

- 41%-60% правильных ответов соответствует пороговому уровню сформированности компетенции на данном этапе ее формирования;

- 61%-80% правильных ответов соответствует продвинутому уровню сформированности компетенции на данном этапе ее формирования;

- 81%-100% правильных ответов соответствует эталонному уровню сформированности компетенции на данном этапе ее формирования.

Сформированность уровня компетенций не ниже порогового является основанием для допуска обучающегося к промежуточной аттестации по данной

#### дисциплине.

Формой промежуточной аттестации по данной дисциплине является экзамен, оцениваемый по принятой в ФГБОУ ВО «РГРТУ» четырехбалльной системе: «неудовлетворительно», «удовлетворительно», «хорошо» и «отлично».

Критерии оценивания текущей успеваемости и промежуточной аттестации представлены в таблице 1.

Таблица 1 Критерии оценивания текущей успеваемости (лабораторные и практические занятия) и промежуточной аттестации (экзамен)

| Шкала оценивания | Критерии оценивания                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------|

| «зачтено»        | студент должен: продемонстрировать общее знание                                                        |

|                  | изучаемого материала; знать основную рекомендуемую                                                     |

|                  | программой дисциплины учебную литературу; уметь                                                        |

|                  | строить ответ в соответствии со структурой излагаемого                                                 |

|                  | вопроса; показать общее владение понятийным                                                            |

|                  | аппаратом дисциплины; уметь устранить допущенные                                                       |

|                  | погрешности в ответе на теоретические вопросы и/или                                                    |

|                  | при выполнении практических заданий под руководством                                                   |

|                  | преподавателя, либо (при неправильном выполнении                                                       |

|                  | практического задания) по указанию преподавателя                                                       |

|                  | выполнить другие практические задания того же раздела                                                  |

|                  | дисциплины.                                                                                            |

| «не зачтено»     | ставится в случае: незнания значительной части                                                         |

|                  | программного материала; не владения понятийным                                                         |

|                  | аппаратом дисциплины; существенных ошибок при                                                          |

|                  | изложении учебного материала; неумения строить ответ в соответствии со структурой излагаемого вопроса; |

|                  | неумения делать выводы по излагаемому материалу.                                                       |

|                  | Оценка «не зачтено» также ставится студентам, которые                                                  |

|                  | не выполнили и защитили лабораторные работы и                                                          |

|                  | практические занятия, предусмотренные рабочей                                                          |

|                  | программой.                                                                                            |

| «отлично»        | «Отлично» заслуживает студент, обнаруживший                                                            |

|                  | всестороннее, систематическое и глубокое знание                                                        |

|                  | учебно-программного материала, умение свободно                                                         |

|                  | выполнять задания, предусмотренные программой,                                                         |

|                  | усвоивший основную и знакомый с дополнительной                                                         |

|                  | литературой, рекомендованной программой. Как правило,                                                  |

|                  | оценка «отлично» выставляется студентам, усвоившим                                                     |

|                  | взаимосвязь основных понятий дисциплины в их                                                           |

|                  | значении для приобретаемой профессии, проявившим                                                       |

|                     | творческие способности в понимании, изложении и       |

|---------------------|-------------------------------------------------------|

|                     | использовании учебно-программного материала.          |

| «хорошо»            | «Хорошо» заслуживает студент, обнаруживший полное     |

|                     | знание учебно-программного материала, успешно         |

|                     | выполняющий предусмотренные в программе задания,      |

|                     | усвоивший основную литературу, рекомендованную в      |

|                     | программе. Как правило, оценка «хорошо» выставляется  |

|                     | студентам, показавшим систематический характер знаний |

|                     | по дисциплине и способным к их самостоятельному       |

|                     | пополнению и обновлению в ходе дальнейшей учебной     |

|                     | работы и профессиональной деятельности.               |

| «удовлетворительно» | «Удовлетворительно» заслуживает студент,              |

|                     | обнаруживший знания основного учебно-программного     |

|                     | материала в объеме, необходимом для дальнейшей учебы  |

|                     | и предстоящей работы по специальности, справляющийся  |

|                     | с выполнением заданий, предусмотренных программой,    |

|                     | знакомый с основной литературой, рекомендованной      |

|                     | программой. Как правило, оценка «удовлетворительно»   |

|                     | выставляется студентам, допустившим погрешности в     |

|                     | ответе на экзамене и при выполнении экзаменационных   |

|                     | заданий, но обладающим необходимыми знаниями для их   |

|                     | устранения под руководством преподавателя.            |

| «не                 | «Неудовлетворительно» выставляется студенту,          |

| удовлетворительно»  | обнаружившему пробелы в знаниях основного учебно-     |

|                     | программного материала, допустившему                  |

|                     | принципиальные ошибки в выполнении                    |

|                     | предусмотренных программой заданий. Как правило,      |

|                     | оценка «неудовлетворительно» ставится студентам,      |

|                     | которые не могут продолжить обучение или приступить к |

|                     | профессиональной деятельности по окончании вуза без   |

|                     | дополнительных занятий по соответствующей             |

|                     | дисциплине.                                           |

# Темы лабораторных работ

- 1. Знакомство с САПР Quartus II. Синтез мультиплексора и семисегментного индикатора.

- 2. Синтез последовательностных цифровых устройств.

- 3. Применение ПЛИС для борьбы с помехами: генератор М-последовательности, фильтр череспериодной компенсации.

- 4. Синтез кодера и декодера кодов Хемминга.

- 5. Синтез цифрового КИХ фильтра на языке VHDL.

6. Изучение протокола передачи данных SPI.

### Контрольные вопросы для защиты лабораторных работ

- 1. Основные элементы и конструкции языка VHDL. Ключевые слова. Идентификаторы. Комментарии. Числа. Строки бит.

- 2. Классификация типов данных в языке VHDL. Основные встроенные типы данных языка VHDL. Понятие подтипа. Пакет std\_logic\_1164.

- 3. Библиотеки и пакеты в языке VHDL. Пользовательские пакеты.

- 4. Интерфейс (сущность) и архитектура объекта в языке VHDL.

- 5. Декларации. Константы в языке VHDL. Глобальные константы. Локальные константы. Настроечная константа GENERIC. Сигналы. Переменные. Присвоение значения переменной и сигналу в языке VHDL. Имя с индексом. Имя-вырезка.

- 6. Процессы в языке VHDL.

- 7. Операции языка VHDL.

- 8. Стили программирования на VHDL. Поведенческий стиль, стиль потоков данных, структурный стиль.

- 9. Оператор COMPONENT. Операторы GENERIC MAP и PORT MAP. Способы подключения портов компонента.

- 10.Последовательные операторы. Оператор IF. Оператор CASE. Оператор NULL. Операторы циклов FOR LOOP и WHILE LOOP. Оператор завершения цикла EXIT.

- 11. Параллельные операторы. Агрегат. Оператор селективного присвоения WITH ... SELECT. Оператор условного назначения сигнала.

- 12. Массивы и записи в языке VHDL.

- 13. Функции в языке VHDL. Функции преобразования типов данных. Пользовательские функции.

- 14.Описание фронта тактового сигнала на языке VHDL. Атрибуты. Синхронные и асинхронные операции в последовательностных цифровых устройствах.

- 15. Конвейерная обработка данных в ПЛИС.

- 16.Описание цифровых конечных автоматов на языке VHDL. Демонстрация графа состояний ЦКА в САПР Quartus II.

- 17. Структура проекта на VHDL. Создание проекта в САПР Quartus II. Отладка VHDL-описаний. Демонстрация структурной схемы проекта средствами САПР Quartus II. Определение максимальной тактовой частоты и времени задержки прохождения сигнала через синтезируемое цифровое устройство средствами САПР Quartus II. Моделирование работы проекта в САПР Quartus II. Подключение отладочного макета и демонстрация работы проекта.

- 18. Описание на языке VHDL и демонстрация работы мультиплексора.

- 19.Описание на языке VHDL и демонстрация работы семисегментного

- индикатора.

- 20.Описание на языке VHDL и демонстрация работы шифратора, приоритетного шифратора, дешифратора.

- 21. Описание на языке VHDL и демонстрация работы компаратора.

- 22. Описание на языке VHDL и демонстрация работы устройства определения количества нулей и/или единиц во входном коде.

- 23. Описание на языке VHDL и демонстрация работы устройства определения чётности/нечётности/кратности входного кода.

- 24. Описание на языке VHDL и демонстрация работы D-триггера.

- 25.Описание на языке VHDL и демонстрация работы N-разрядного параллельного регистра.

- 26.Описание на языке VHDL и демонстрация работы суммирующего/вычитающего/реверсивного счётчика.

- 27. Описание на языке VHDL и демонстрация работы делителя частоты.

- 28.Описание на языке VHDL и демонстрация работы ШИМ-модулятора.

- 29.Описание на языке VHDL и демонстрация работы сторожевого таймера Watch-Dog.

- 30.Описание на языке VHDL и демонстрация работы последовательного Nразрядного регистра.

- 31.Описание на языке VHDL и демонстрация работы генератора Мпоследовательности по заданному характеристическому полиному. Реализация генератора М-последовательности с помощью сигнала и с помощью переменной.

- 32. Описание на языке VHDL и демонстрация работы обнаружителя семиэлементной М-последовательности на основе согласованного фильтра.

- 33.Описание на языке VHDL и демонстрация работы фильтра череспериодной компенсации n-го порядка.

- 34. Описание на языке VHDL и демонстрация работы цифрового КИХ фильтра n-го порядка.

- 35.Описание на языке VHDL и демонстрация работы кодера и декодера кодов Хемминга. Анализ функциональных схем синтезируемых цифровых устройств. Анализ быстродействия различных конвейерных реализаций декодера кода Хемминга.

- 36.Описание на языке VHDL цифрового конечного автомата (ЦКА) для обмена данными по протоколу SPI на примере аналого-цифрового преобразователя (АЦП) AD7705.

# Темы практических занятий

- 1. Составление VHDL-описания сущности на языке VHDL.

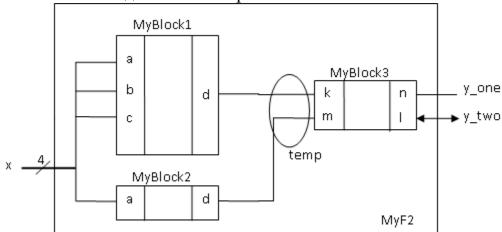

- 2. Сигналы и компоненты. Составление программы с применением структурного стиля программирования.

- 3. Синхронные и асинхронные операции в последовательностных

цифровых устройствах.

- 4. Синтез параметрических счетчиков.

- 5. Параллельное и каскадное подключение нескольких однотипных компонентов к проекту верхнего уровня.

- 6. Синтез генератора М-последовательности с входами управления.

- 7. Цифровые конечные автоматы.

- 8. Кодеры и декодеры помехоустойчивых кодов.

- 9. Пользовательские пакеты и функции в языке VHDL.

- 10.Составление управляющих байтов для записи в регистры управления AD7705.

# Примеры задач для практических занятий

1. Составить описание на языке VHDL цифрового устройства **с помощью структурного стиля программирования**. При подключении компонентов в содержательной части архитектуры применить и позиционное и поименованное подключение портов.

- 2. Составить описание на языке VHDL **D-триггера** с входами асинхронной установки *Set* и синхронного сброса *Reset*.

- 3. Составить описание на языке VHDL параллельного N-разрядного регистра с входом синхронного сброса Reset (активное значение высокий логический уровень). Параметр N=10 определить как глобальную константу, которая задается в пакете. Работа устройства происходит по заднему фронту тактового импульса.

- 4. Составить описание на языке VHDL **суммирующего счетчика** с входом асинхронного сброса *Reset* (активное значение низкий логический уровень, по которому счетчик принимает минимальное значение) и входом тактовых импульсов *clk* (счётчик меняет своё состояние по переднему фронту тактового импульса). Модуль счета  $K_{cq} = 12$ .

- 5. Составить описание на языке VHDL **архитектуры** делителя частоты с коэффициентом деления 128, используя **только** существующий модуль делителя частоты с фиксированным коэффициентом деления 2, описание

#### которого имеет вид:

```

entity Div_freq_2 is port (c_in: in std_logic; -- входной сигнал clk: out std_logic -- выходной сигнал); end Div_freq;

```

- 6. Составить описание на языке VHDL последовательного *N*-разрядного регистра с входом асинхронного сброса *Reset* (активное значение высокий логический уровень). Параметр *N* определить как настроечную константу *Generic*. В качестве выходных портов определить параллельный код (содержимое всего регистра) и бит из последнего триггера регистра.

- 7. Составить описание на языке VHDL генератора М-последовательности с порождающим полиномом  $P(x) = 1 + x + x^3$  с входом разрешения асинхронной параллельной загрузки Load (активное значение высокий логический уровень) стартовой комбинации  $Start\_data$ . Стартовую комбинацию  $Start\_data$  подавать на отдельный входной порт. Работу устройства организовать по переднему фронту тактовых импульсов clk.

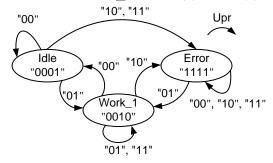

- 8. Составить описание на языке VHDL **цифрового автомата** с тактовым сигналом *clk*, входным двухразрядным логическим сигналом *Upr*, выходным четырехразрядным сигналом *Data\_out* и заданной диаграммой состояний.

9. Составить описание на языке VHDL цифрового автомата, описывающего 3-разрядный счетчик кода Грея с выходными сигналами  $000->001->011->111->110->100->000->\dots$  и входом асинхронного сброса *reset*.

# Вопросы к экзамену

- 1. Лексические элементы языка VHDL

- 2. Типы данных в VHDL. Функции преобразования типа

- 3. Тип std\_logic

- 4. Объекты VHDL. Описание сущности

- 5. Архитектура объекта в VHDL

- 6. Сигналы и процессы

- 7. Операции в языке VHDL. Приоритет операций

- 8. Структурный стиль описания объектов. Подключение проекта к проекту верхнего уровня. Позиционное и поименованное присвоение

- 9. Агрегат. Имя с индексом и имя-вырезка

- 10. Переменные в VHDL. Разница между переменной и сигналом

- 11. Пакеты в VHDL. Подключение пакета к проекту.

- 12. Константы в VHDL. Настроечная константа GENERIC. Описание сущности с настроечной константой.

- 13.Операторы If и Case

- 14. Операторы цикла For...Loop и While...Loop, оператор Exit

- 15.Параллельные операторы языка VHDL (With...Select, оператор условного назначения сигнала, оператор генерации Generate)

- 16. Функции в VHDL

- 17. Массивы и записи в языке VHDL

- 18.Описание фронта тактового сигнала на языке VHDL. Управляющие сигналы. Синхронные и асинхронные действия.

- 19. Цифровые автоматы и их описание с использованием операторов процесса. Описание автомата с использованием графа (диаграммы состояний).

- 20. Цифровые автоматы и их описание с использованием операторов процесса. Описание автомата с помощью совмещённой таблицы переходов и выходов.

- 21. Конвейерная обработка на ПЛИС

- 22. Архитектура ПЛИС типов CPLD и FPGA. Преимущества и недостатки

- 23.Интерфейс JTAG

- 24. Протокол RS-232. Основные характеристики. Чётность. Временная диаграмма сигнала в линии при передаче байта данных.

- 25.Протокол RS-485. Основные характеристики. Шина данных RS-485. Подключение устройств к шине RS-485.

- 26.Протокол SPI. Основные характеристики. Подключение устройств к шине SPI. Режимы работы интерфейса SPI.

- 27. Протокол SPI. Основные характеристики. Приём и передача данных по протоколу SPI.

- 28.Протокол 1-Wire. Основные характеристики. Нормальное и паразитное питание. Подключение устройств к шине 1-Wire

- 29. Импульсы RESET и PRESENCE протокола 1-Wire. Тайм-слоты передачи.

- 30.Импульсы RESET и PRESENCE протокола 1-Wire. Тайм-слоты приёма.

# Темы задач к экзамену

- 1. Сигналы и компоненты (Структурный стиль описания объектов)

- 2. Процессы. Синхронные и асинхронные операции (D-триггер, N-разрядный параллельный регистр, Счётчик, Сторожевой таймер)

- 3. Генераторы М-последовательностей (Последовательный N-разрядный регистр, Генератор М-последовательности)

- 4. Параллельный оператор Generate (Подключение компонентов при помощи оператора Generate)

- 5. Кодеры и декодеры помехоустойчивых кодов (Кодер и декодер кода Хемминга)

- 6. Шифратор, дешифратор

- 7. Делитель частоты, ШИМ-модулятор

- 8. Цифровые конечные автоматы

### Контрольные вопросы для оценки сформированности компетенций

- 1. Разрешенные идентификаторы в VHDL.

- 2. Тип std\_logic.

- 3. Объявление сущности в VHDL.

- 4. Настроечные константы в VHDL.

- 5. Описание архитектуры в VHDL.

- 6. Какие элементы объявляются в декларативной части архитектуры программы?

- 7. Сигналы в VHDL.

- 8. Процессы в VHDL.

- 9. Какие элементы объявляются в декларативной части процесса?

- 10. Можно ли объявить внутри процесса сигнал? Почему?

- 11. Можно ли объявить внутри процесса другой процесс? Почему?

- 12. Поименованное и позиционное подключение портов компонента.

- 13. Последовательные операторы языка VHDL.

- 14. Параллельные операторы языка VHDL.

- 15. Синхронные и асинхронные действия.

- 16. Описание триггеров и регистров на языке VHDL.

- 17. Пакеты в VHDL.

- 18. Массивы и записи в VHDL.

- 19. Цифровые автоматы Мура и Мили.

|    | Контрольные задания для оценки остаточных знании по предмету |

|----|--------------------------------------------------------------|

| 1. | Выберите все возможные идентификаторы в языке VHDL:          |

|    | 1. My_Logic                                                  |

|    | 2. 2Trig                                                     |

|    | 3. ТеМР_Щ                                                    |

|    | 4. TeMp12                                                    |

|    | 5. entity                                                    |

|    | 6. automat_12                                                |

|    |                                                              |

|    | Номера правильных ответов: <u>1 4 6</u>                      |

| 2. | Выберите все возможные идентификаторы в языке VHDL:                     |

|----|-------------------------------------------------------------------------|

|    | 1. константа                                                            |

|    | 2. VHDL_1                                                               |

|    | 3. Count111                                                             |

|    | 4. out                                                                  |

|    | 5my_auto                                                                |

|    | 6. MUX                                                                  |

|    |                                                                         |

|    | Номера правильных ответов: _2_3_6                                       |

| 3. | Выберите все возможные идентификаторы в языке VHDL:                     |

|    | 1. Zadacha_6                                                            |

|    | 2. inout                                                                |

|    | 3. architecture                                                         |

|    | 4. Clk                                                                  |

|    | 5. Segment7                                                             |

|    | 6. 22mux                                                                |

|    |                                                                         |

|    | Номера правильных ответов: 1_4_5                                        |

| 4. | Какой перечисляемый тип данных используется для описания входных и      |

|    | выходных одноразрядных сигналов, проектируемого на языке VHDL,          |

|    | цифрового устройства?                                                   |

|    | Hannary was among and looks                                             |

|    | Правильный ответ: std_logic                                             |

| 5. | Какой перечисляемый тип данных используется для описания входных и      |

|    | выходных многоразрядных сигналов, проектируемого на языке VHDL,         |

|    | цифрового устройства?                                                   |

|    | Правильный ответ: std_logic_vector                                      |

| 6. | О каком понятии идёт речь? «Описывает внешний интерфейс объекта         |

|    | (моделирует взгляд на устройство <i>«снаружи»</i> ) и содержит описание |

|    | входных и выходных сигналов – портов»                                   |

|    |                                                                         |

|    | Правильный(ые) ответ(ы): Сущность/Сущность объекта/Entity               |

| 7. | Какое ключевое слово используется для определения сущности объекта в    |

|    | языке VHDL?                                                             |

|    |                                                                         |

|    | Правильный ответ: entity                                                |

| 8.  | Какое ключевое слово используется для определения настроечных констант в языке VHDL?                                                                                                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Правильный ответ: generic                                                                                                                                                                 |

| 9.  | О каком понятии идёт речь? «Определяет логику работы проектируемого цифрового устройства и форму её реализации (моделирует взгляд на объект <b>«изнутри»</b> )»                           |

|     | Правильный(ые) ответ(ы): Архитектура/Архитектура объекта/Architecture                                                                                                                     |

| 10. | Какое ключевое слово используется для определения архитектуры объекта в языке VHDL?                                                                                                       |

|     | Правильный ответ: architecture                                                                                                                                                            |

| 11. | Выберите правильный ответ: Декларативная часть архитектуры <b>HE может</b> содержать объявление: 1. Сигнала 2. Переменной 3. Константы 4. Компонента                                      |

|     | Правильный ответ: 2                                                                                                                                                                       |

| 12. | О каком понятии идёт речь? «Это элемент языка VHDL, который переносит значение от одного объекта или процесса к другому объекту или процессу и вместе с ним синхронизирующее воздействие» |

|     | Правильный(ые) ответ(ы): Сигнал/Signal                                                                                                                                                    |

| 13. | Какое ключевое слово используется в языке VHDL для объявления сигнала?  1. entity 2. architecture 3. begin 4. signal 5. variable 6. constant                                              |

|     | Номер правильного ответа: $_{\underline{4}}$                                                                                                                                              |

| 14. | О каком понятии идёт речь? «Это основной параллельный оператор языка VHDL, который используется для поведенческой формы описания проектов»                                                |

|     | Правильный(ые) ответ(ы): Процесс/Process                                                                                                                                                  |

| 15. | Выберите правильный ответ:                                           |

|-----|----------------------------------------------------------------------|

|     | Декларативная часть процесса НЕ может содержать объявление:          |

|     | 1. Сигнала                                                           |

|     | 2. Переменной                                                        |

|     | 3. Константы                                                         |

|     | 4. Функции                                                           |

|     |                                                                      |

|     | Правильный ответ: 1                                                  |

| 16. | Какой оператор языка VHDL предназначен для последовательного выбора  |

|     | вариантов?                                                           |

|     | 1. if                                                                |

|     | 2. case                                                              |

|     | 3. for loop                                                          |

|     | 4. port map                                                          |

|     | 5. component                                                         |

|     | 6. <= (ПУ3C)                                                         |

|     |                                                                      |

|     | Правильный ответ: 1                                                  |

| 17. | Какой оператор языка VHDL предназначен для множественного выбора?    |

|     | 1. if                                                                |

|     | 2. case                                                              |

|     | 3. for loop                                                          |

|     | 4. port map                                                          |

|     | 5. component                                                         |

|     | $6. <= (\Pi V3C)$                                                    |

|     |                                                                      |

|     | Правильный ответ: 2                                                  |

| 18. | Какой оператор языка VHDL необходим для присвоения значения сигналу? |

|     | 1. if                                                                |

|     | 2. case                                                              |

|     | 3. for loop                                                          |

|     | 4. port map                                                          |

|     | 5. component                                                         |

|     | 6. <= (ПУЗС)                                                         |

|     |                                                                      |

|     | Правильный ответ: 6                                                  |

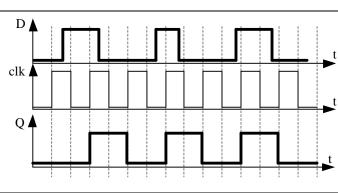

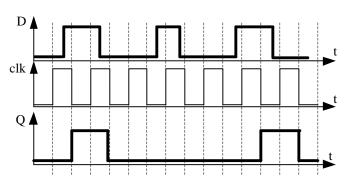

19. Какой оператор языка VHDL используется для объявления экземпляров объектов нижнего уровня, из которых состоит проект верхнего уровня? 1. if 2. case 3. for loop 4. port map 5. component 6. <= (ПУЗС) Правильный ответ: 5 Какой оператор языка VHDL необходим для реализации межкомпонентных 20. связей в проекте структурной формы? 1. if 2. case 3. for loop 4. port map 5. component 6.  $<= (\Pi Y 3C)$ Правильный ответ: 4 Какая конструкция в языке VHDL используется для описания переднего 21. фронта тактового сигнала clock? Правильный ответ: clock'event and clock = '1' 22. Какая конструкция в языке VHDL используется для описания заднего фронта тактового сигнала clk? Правильный ответ: clk'event and clk = '0'23. Изобразите временную диаграмму процесса на выходе **D-триггера**, работающего по переднему фронту тактового сигнала: D clk Q 🌢 Правильный ответ:

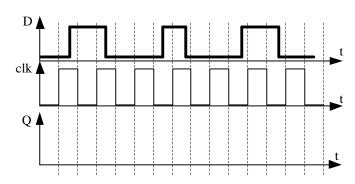

24. Изобразите временную диаграмму процесса **на выходе D-триггера**, работающего **по заднему фронту** тактового сигнала:

Правильный ответ:

25. Каким термином в языке VHDL называют действие, происходящее по фронту таксового сигнала?

Правильный ответ: синхронное

26. Каким термином в языке VHDL называют действие, происходящее независимо от прихода фронта тактового сигнала?

Правильный ответ: асинхронное

- 27. Какой пакет необходимо подключить к проекту для возможности использования арифметических операций?

- 1. std\_logic\_1164

- 2. std\_logic\_arith

|     | 3. std_logic_signed                                           |

|-----|---------------------------------------------------------------|

|     | 4. std_logic_unsigned                                         |

|     |                                                               |

|     | Правильный ответ: 2                                           |

| 28. | Какой пакет необходимо подключить к проекту для возможности   |

|     | использования типов данных std_logic и std_logic_vector?      |

|     | 1. std_logic_1164                                             |

|     | 2. std_logic_arith                                            |

|     | 3. std_logic_signed                                           |

|     | 4. std_logic_unsigned                                         |

|     |                                                               |

|     | Правильный ответ: 1                                           |

| 29. | Какой пакет необходимо подключить к проекту для возможности   |

|     | использования функций преобразования типов и чисел со знаком? |

|     | 1. std_logic_1164                                             |

|     | 2. std_logic_arith                                            |

|     | 3. std_logic_signed                                           |

|     | 4. std_logic_unsigned                                         |

|     | П                                                             |

| 20  | Правильный ответ: 3                                           |

| 30. | Какой пакет необходимо подключить к проекту для возможности   |

|     | использования функций преобразования типов и чисел без знака? |

|     | 1. std_logic_1164                                             |

|     | 2. std_logic_arith                                            |

|     | 3. std_logic_signed                                           |

|     | 4. std_logic_unsigned                                         |

|     | Правильный ответ: 4                                           |

| i   | TIPODINIDITI OTDET. T                                         |

Составил

Ст.преподаватель кафедры РТС

/ Т.С. Кислицына