#### ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ

#### РЯЗАНСКАЯ ГОСУДАРСТВЕННАЯ РАДИОТЕХНИЧЕСКАЯ АКАДЕМИЯ

# ПРОЕКТИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ НА ОСНОВЕ САПР ФИРМЫ XILINX

Методические указания к лабораторным работам

УДК 621.315.6

Проектирование цифровых устройств на основе САПР фирмы Xilinx: Методические указания к лабораторным работам / Рязан. гос. радиотехн. акад.; Сост.: В.Н. Локтюхин, С.В. Челебаев, Н.В. Шемонаев. Рязань, 2005. 24 с.

Изложены краткие теоретические сведения и основы методов проектирования цифровых схем на основе ПЛИС фирмы Xilinx. Рассмотрено проектирование счетчиков, регистров и других устройств на основе ПЛИС.

Предназначены для студентов направления 200100.

Табл. 5. Ил.17. Библиогр.: 5 назв.

Проектирование, цифровые схемы, ПЛИС, Xilinx, САПР

Печатается по решению методического совета Рязанской государственной радиотехнической академии.

Рецензент: кафедра биомедицинской и полупроводниковой электроники РГРТА (зав. кафедрой С.В. Вихров)

Проектирование цифровых устройств на основе САПР фирмы Xilinx Составители: Локтюхин Виктор Николаевич Челебаев Сергей Владимирович Шемонаев Николай Викторович

Редактор Е.В. Ипатова Корректор С.В. Макушина

Подписано в печать . Формат бумаги 60х84 1/16. Бумага газетная. Печать трафаретная. Усл. печ. л. 1,5. Уч.-изд. л. 1,5. Тираж 30 экз. Заказ Рязанская государственная радиотехническая академия. 390005, Рязань, ул. Гагарина, 59/1. Редакционно-издательский центр РГРТА.

# ЛАБОРАТОРНАЯ РАБОТА № 1 ОСВОЕНИЕ ПАКЕТА ПРИКЛАДНЫХ ПРОГРАММ ФИРМЫ XILINX

**Цель работы:** ознакомиться с возможностями пакета прикладных программ фирмы Xilinx, научиться исследовать простые логические схемы.

# 1. Подготовка к работе

Перед началом работы следует ознакомиться с описанием, для этого необходимо изучить рекомендуемую литературу и приложение к данному пособию.

#### 2. Теоретические сведения

#### 2.1. Запуск нового проекта

- Запустите *Project Manager* двойным нажатием иконки (*Active-Cad*) в группе иконок *Active-Cad*.

- Когда появится окно *Project Manager*, нажмите иконку (*New Project*) для вызова окна *New Project*.

- Введите имя проекта, его каталог и тип в окне *New Project*. Некоторые типы проектов позволяют выбирать также семейство, номер детали и скорость устройства.

- Запустите схемный редактор нажатием кнопки *Schematic Editor* в окне *Project Manager*. Редактор откроет в своем окне новый схемный лист (.sch). Его имя будет тем же, что и имя текущего проекта.

#### 2.2. Построение схемы

# 2.2.1. Рамка страницы и таблица

Схема может содержать много листов (страниц), которые могут создаваться командой *New Sheet* в меню *File*. Вы можете чертить схему на новой странице сразу после ее создания. Размер и рамка нового листа и его имя по умолчанию те же, что в текущем проекте. Они могут быть изменены с помощью опции *Page Setup* в меню *File*. Используя поля *Frame*, *Sheet Format* и *Ruler* вы можете определить:

- включение/выключение рамки и число зон на странице;

- размер листа (А-Е, А0-А4, любой размер);

- ориентация листа (портрет или ландшафт);

- начало координатных осей.

Active-Cad позволяет заказывать таблицу проекта, которая отображается и печатается в правом нижнем углу листа схемы. Для заказа таблицы используйте опцию  $Table\ Setup$ .

#### 2.2.2. Обозначения и компоненты

Каждое обозначение содержит графическую часть, имя компоненты, ее тип и атрибуты. Для поиска желаемого компонента нажмите любое

обозначение для вызова подсвечиваемого курсора. Далее пройдитесь по списку с помощью клавиш курсора или прямоугольника скроллинга. Если вы знаете имя обозначения, напечатайте его в строке редактирования внизу справа в окне SC Symbols. Подсвеченный курсор укажет на первое подходящее обозначение в списке. Для помещения на схеме нового элемента войдите в режим Symbol нажатием клавиши F2 или иконки Symbol Toolbox. Обозначение из окна библиотеки автоматически появится на правой стороне экрана. Переместите обозначение, связанное с курсором мыши, в желаемую позицию и нажмите левую клавишу мыши. Когда вы выведите обозначение схема будет автоматически прокручиваться за пределы окна, средств авто-панорамирования. Для помещения управлением компонента на схему выберите его в окне SC Symbols и повторите процедуру размещения компонента.

#### 2.2.3. Соединения (провода или шины)

Проводные соединения могут быть начерчены:

- от контакта до контакта;

- от контакта до терминала ввода- вывода;

- от контакта к существующему проводному соединению и наоборот.

Вы можете закончить провод в любой позиции двойным нажатием кнопки мыши. Это произведет фиктивный терминал, также называемый концом провода (wire-end), который выглядит как кружек или маленький квадрат с красным крестиком внутри.

Все соединения действительны, пока они вычерчиваются, редактор не разрешает начинать или заканчивать провод, который не представляет действительного электрического соединения. Это ограничение - следствие подчиненной имитации системы *Active-Cad*.

#### 2.2.4. Точки подключения питания

Активизируйте иконку *Power Symbol. Active-Cad* отобразит окно для выбора сигнала питания и его графического представления. Сделайте выбор и нажмите Ok. Курсор будет сопровождать маленький квадратик. Поместите его на желаемый контакт или провод и нажмите клавишу мыши. Произойдет подсоединение источника, если вместо Ok нажать Repeat.

#### 2.2.5. Имена терминалов (клемм, зажимов) и схем

Имена схем используются для наименования проводов (узлов) на схеме. Все схемы, использующие одинаковые имена, объединяются в одну. Вначале проводам присваиваются скрытые имена. Они используются внутри *Active-Cad* для прокладки проводов. Однако для пояснения и документирования вы можете дать имя каждому проводу на схеме.

Для добавления имени к существующему проводу используется следующая процедура

- Нажмите иконку Add Net or Bus Name.

- Когда появится окно *Net Name*, введите имя и нажмите *Ok*.

- При курсоре появится красный прямоугольник. Переместите его в позицию, где должно быть помещено имя, и нажмите клавишу мыши. Имя схемы будет помещено около провода. С другой стороны, оно отобразится другим цветом (зеленым), в отличие от имени схемы (синий), и не будет представлено проводу. Изменение цвета в меню *Preference* изменит ранее описанные цвета.

<u>Примечание</u>. Каждый узел может иметь только одно имя. Если вы попытаетесь соединить две схемы с одинаковыми именами, на схеме появится предупреждение. Вы должны изменить или удалить одно из имен перед соединением двух схем.

Если вы попытаетесь присвоить новое имя уже поименованному проводу, будет выдано предупреждение, а операция отменена. Вы можете присвоить новое имя только после удаления первоначального.

Для изменения имени дважды нажмите имя схемы и, когда появится окно *Net Name*, редактируйте имя.

Для удаления имени схемы выберите имя и нажмите клавишу *Delete*.

Для передвижения имени схемы включите режим *Select*, нажмите имя схемы и переместите его в желаемую позицию.

# 2.2.6. Графика и текст

Графический редактор выбирается иконкой  $Grafics\ Toolbox\$ или клавишей F6. Вычерчиваемые элементы не имеют электрических параметров и не проверяются по электрическим правилам. Опции графического редактора:

- *Line* чертит единственную линию;

- Polyline чертит многосегментные линии;

- Ortholine чертит только горизонтальные или вертикальные линии;

- Rectangle чертит прямоугольник по выбранным диагональным углам;

- *Circle* чертит круг с выбранным центром и вытягиванием (*stretching*) его внешней линии;

- Arc чертит дугу путем выбора конечных точек и проведением внешней линии;

- *Text* создание и размещение строк текста на схеме;

- Text Style установка размера текста, шрифта и цвета;

- Line Style установка формы линии, цвета и толщины.

Каждая операция редактирования графики начинается и заканчивается нажатием левой клавиши мыши. Вы можете приостановить текущий режим нажатием правой клавиши мыши с последующим выбором иконки *End* в панели инструментов *SC Graphics*.

#### 2.3. Внесение изменений в схему

#### 2.3.1. Выбор области схемы

Для просмотра специфичной области схемы используйте опции:

- увеличить выбранную область;

- увеличить полный лист схемы;

- обменять текущую страницу с изображением полной страницы;

- поместить выбранную область в центр изображения схемы.

#### 2.3.2. Увеличение в выбранной области

Выберите иконку *Zoom Area* в верхнем прямоугольнике и переместите ее в угол, противоположный углу выбранной области. При освобождении клавиши мыши отмеченная область распространится на весь экран.

Для увеличения внутри выбранной области нажмите на один из углов увеличиваемой области и нажмите одновременно клавишу мыши и *CTRL*. Удерживая клавишу мыши нажатой, переместите курсор в противоположный угол увеличиваемой области. Отмеченный прямоугольник отображается во время операции для отметки выбранной области. Когда желаемая область окажется внутри прямоугольника, освободите клавишу мыши. Выбранная область расширится на весь экран.

Для центрирования выбранной области на изображении схемы необходимо нажать F9 или выбрать опцию Center в меню Display. В ответ Active-Cad отобразит курсор в виде прицела. Если вы нажмете левую клавишу мыши, область под курсором отобразится в центре экрана.

#### 2.3.3. Дублирование обозначений

При активной иконке *Symbol Toolbox* нажатие на любое обозначение производит его копию (дубликат), который следует за курсором мыши. Вы можете поместить дубликат в любую позицию экрана нажатием на клавишу мыши. Это разрешено, если схема находится в только режиме *Symbol* (размещение), и никакое другое обозначение не представлено курсору. Если обозначение представлено курсору, нажмите правую клавишу мыши для освобождения существующего обозначения, а затем нажмите на желаемое обозначение, которое вы хотите скопировать. Каждое помещенное обозначение получит свой ссылочный номер.

# 2.3.4. Нумерация обозначений

Все обозначения автоматически именуются при помещении в схему. Имя состоит из текстовой строки и числового суффикса, который

увеличивается каждый раз, когда вы помещаете обозначение. Для переименования детали выберите опцию *Annotation* в меню *Options*.

#### 2.3.5. Поворот (вращение) обозначений

Для вращения по часовой стрелке отдельного обозначения нажмите клавиши Ctrl+L, пока обозначение представлено курсору. Каждое нажатие поворачивает обозначение на  $90^{\circ}$ . Нажатие Ctrl+M порождает зеркальное отражение обозначения.

Если обозначение уже помещено на схеме, подсветите его в режиме *Select* и нажмите иконку *Properties*. Это вызовет окно *Edit Symbol*. В окне *Edit Symbol* выберите опцию *Attributes*, выберите желаемый поворот компоненты.

#### 2.3.6. Удаление обозначений

Для удаления обозначений, только что введенных, нажмите клавишу *Del* на панели. По каждому нажатию удаляется по одному обозначению в порядке, обратном их вводу в схему. Операция удаления запрещена только, когда вы выходите из режима *Symbol Toolbox*. Возврат обратно в этот режим не восстанавливает опцию удаления.

Вы можете удалить любое обозначение, терминал или провод в режиме *Select*. Для удаления элемента, выберите его нажатием клавиши мыши и тогда нажмите клавишу *Del* на панели или воспользуйтесь опцией *Delete* в меню *Edit*. Если вы ошибочно удалили обозначение, можете восстановить его нажатием опции *Undo* в меню *Edit*.

# 2.3.7. Сохранение проекта

Для того чтобы сохранить проект необходимо выбрать опцию File: Save (комбинация клавиш Ctrl-S) или нажать соответствующую иконку на горизонтальной панели редактора.

# 3. Порядок выполнения работы

- 1. Получить у преподавателя вариант задания согласно номеру бригады (см. таблицу), провести минимизацию функции.

- 2. Сформировать логическую схему.

- 3. Сформировать полученную логическую схему с помощью пакета прикладных программ.

- 4. Представить отчет о работе: распечатка логической схемы и результатов моделирования.

# Варианты заданий к лабораторной работе № 1

| Nº | Варианты заданий                                                                      |  |

|----|---------------------------------------------------------------------------------------|--|

| 1  | $f = x_1 \overline{x}_2 x_3 x_4 + x_1 \overline{x}_3 + x_2 x_4$                       |  |

| 2  | $f = x_1 x_2 x_4 + x_2 \overline{x}_3 + \overline{x}_1 \overline{x}_2 \overline{x}_3$ |  |

| 3  | $f = \overline{x}_1 x_2 + x_3 x_4 + \overline{x}_2 \overline{x}_3 x_4$                |  |

| 4  | $f = x_1 \bar{x}_3 + \bar{x}_3 x_4 + \bar{x}_1 \bar{x}_2 x_3$                         |  |

| 5  | $f = \overline{x}_1 x_3 + \overline{x}_1 x_2 \overline{x}_3 + x_2 \overline{x}_4$                           |

|----|-------------------------------------------------------------------------------------------------------------|

| 6  | $f = \overline{x}_1 x_2 x_3 + x_1 \overline{x}_3 + \overline{x}_2 x_3 \overline{x_4}$                       |

| 7  | $f = \overline{x}_1 \overline{x}_3 x_4 + x_2 x_3 + x_1 + \overline{x}_2 x_4$                                |

| 8  | $f = \overline{x}_{2}\overline{x}_{3} + \overline{x}_{1}x_{3}x_{4} + x_{1}x_{2}\overline{x_{4}}$            |

| 9  | $f = x_1 x_2 \overline{x}_3 + \overline{x}_1 x_2 x_4 + x_3 \overline{x_4} x_2$                              |

| 10 | $f = \overline{x_1} x_2 \overline{x_4} + \overline{x_1} \overline{x_2} \overline{x_3} + x_2 \overline{x_4}$ |

#### ЛАБОРАТОРНАЯ РАБОТА № 2

# МОДЕЛИРОВАНИЕ КОМБИНАЦИОННЫХ ЦИФРОВЫХ УСТРОЙСТВ

**Цель работы:** обучение методике проектирования комбинационных цифровых устройств, закрепление навыков применения ППП фирмы Xilinx.

# 1. Теоретические сведения

Перед началом работы рекомендуется изучить теорию, представленную в рекомендуемой литературе по принципам синтеза комбинационных схем.

#### Методика структурного проектирования комбинационных схем

Комбинационными схемами называются цифровые устройства, логическое состояние выходов которых зависит только от комбинации логических сигналов на входах в данный момент времени.

Исходными данными для проектирования комбинационной схемы являются его функциональное описание и требования к основным электрическим параметрам. Функциональное описание комбинационной схемы обычно дается в виде таблицы истинности или алгебраического выражения. На стадии структурного проектирования получается наиболее простое (минимизированное) логическое выражение заданной функции и строится соответствующая ему структурная схема на заданной или выбранной элементной базе. Процесс структурного проектирования разбивается на несколько последовательно выполняемых этапов.

# 1. Минимизация заданной логической функции.

Чем проще логическое выражение реализуемой функции, тем меньше элементов требуется для ее выполнения. В результате микросхема, выполняющая эту функцию, будет иметь лучшие показатели по быстродействию, потребляемой мощности, площади кристалла.

В алгебре логики разработаны методы минимизации логических функций. Для минимизации функций относительно небольшого числа переменных  $(k \le 6)$  наиболее простым и наглядным является графический

метод, использующий карты Карно. Для функций большего числа переменных (k>6) можно декомпозицией выделить более простые составляющие функции с числом переменных не более 6, которые минимизируются с помощью карт Карно.

При использовании этого метода исходная логическая (или переключательная) функция представляется на карте Карно. Минтермы, соответствующие двум соседним (в столбце или ряду) клеткам карты Карно, отличаются значениями только одной переменной. Поэтому дизъюнкция этих двух минтермов дает один конъюнктивный член, в котором исключена общая переменная [3].

Чтобы выделить клетки, представляющие один конъюнктивный член, их графически объединяют — обводят на карте Карно тонкой линией. Таким образом, конъюнктивный член представляется на картах Карно двумя объединенными клетками. Такое объединение клеток на картах Карно эквивалентно выполнению данного ранее логического преобразования и позволяет получить более простое выражение логической функции. Объединенные клетки будут соответствовать конъюнктивным членам, дизъюнкция которых даст минимизированную дизъюнктивную нормальную форму (МДНФ) заданной функции.

# 2. Построение структурной схемы проектируемой микросхемы в соответствии с полученными МДНФ или МКНФ

При этом полученные логические выражения сначала следует представить в виде комбинации операций, выполняемых элементами базового набора, а затем построить логическую структуру схемы. Базовые элементы современных цифровых микросхем выполняют операции И —  $HE, UJU - HE, U - UJU - HE, HE и Монтажное И (И^2J), ИJИ - HE и Монтажное ИЛИ (ЭСЛ).$

# Примеры типичных комбинационных схем

# 1. Шифраторы и дешифраторы

Одними из основных видов преобразования информации в цифровых системах является *шифрация и дешифрация*. Шифрацией называется преобразование M-разрядного двоичного кода, имеющего  $K_{M}$  безразличных наборов входных переменных, в однозначно соответствующий ему n-разрядный код, имеющий меньшее число разрядов n < M и безразличных наборов  $K_{n} < K_{M}$ . Таким образом, при шифрации каждому из  $(2^{M} - K_{M})$  рабочих наборов входных переменных ставится в соответствие один из  $(2^{n} - K_{n})$  рабочих наборов выходных переменных, т. е.  $(2^{M} - K_{M}) = (2^{n} - K_{n})$ . В результате шифрации осуществляется «сжатие» информации для передачи но меньшему числу линий связи (n < M) за счет полного (при  $K_{n} = 0$ ) или частичного (при  $K_{n} \neq 0$ ) исключения безразличных наборов. Обратное

преобразование, т. е. восстановление информации в первоначальном M-разрядном коде с  $K_{M}$  избыточными комбинациями, называется дешифрацией. Функциональные узлы для выполнения этих операций называются mudpamopamu и demudpamopamu. Они различаются по числу входов и выходов и называются «шифратор (дешифратор) из M в n (из n в M)». Максимальное число входов шифратора не превышает количество возможных комбинаций выходных сигналов:  $M < 2^m$ . Соответственно для дешифратора число выходов  $n \le 2^m$  [3]. Дешифратор реализует на выходах минтермы входных переменных или инверсии минтермов — макстермы.

#### 2. Мультиплексоры и демультиплексоры

Mультиплексором называется функциональный узел, обеспечивающий передачу информации, поступающей по нескольким входным линиям связи, на одну выходную линию. Выбор той или иной входной линии  $A_i$  осуществляется в соответствии с поступающим адресным кодом  $S_0S_1$ ... При наличии n адресных входов можно реализовать  $M=2^n$  комбинаций адресных сигналов  $S_i$ , каждая из которых обеспечивает выбор одной из M входных линий. Чаще всего используются мультиплексоры «из 4 в 1» (M=4, n=2), «из 8 в 1» (M=4, n=3), «из 16 в 1» (M=16, n=4). Если допустить наличие избыточных комбинаций адресных сигналов, то можно спроектировать мультиплексоры с любым числом входных линий  $M \le 2^n$ .

Для восстановления мультиплексированной информации используются демультиплексоры, которые в соответствии с принятым адресом направляют информацию в одну из M выходных линий связи. При этом на остальных линиях поддерживается логический "0".

Мультиплексоры и демультиплексоры могут быть реализованы на элементах различных типов путем выполнения логических выражений.

# 2. Порядок выполнения работы

- 2.1. Получить у преподавателя вариант задания согласно номеру бригады (см. таблицу).

- 2.2. В соответствии с заданием сформировать таблицу истинности требуемого устройства.

- 2.3. На основании этой таблицы получить необходимые СДНФ.

- 2.4. С помощью карт Карно провести минимизацию полученных СДНФ.

- 2.5. На основании полученных в результате минимизации МДНФ, построить структурную схему устройства.

- 2.6. Сформировать полученную схему с помощью ППП.

- 2.7. Провести исследование заданной схемы и убедиться в правильности ее работы.

- 2.8. Представить отчет: распечатка логической схемы и результатов моделирования.

#### Варианты заданий к лабораторной работе № 2

| №  | Варианты заданий                  |        |  |

|----|-----------------------------------|--------|--|

|    | Логическая схема                  | Базис  |  |

| 1  | Шифратор "из 10 в 4"              | И-НЕ   |  |

| 2  | Шифратор "из 10 в 4"              | ИЛИ-НЕ |  |

| 3  | Дешифратор "из 4 в 10"            | И-НЕ   |  |

| 4  | Дешифратор "из 4 в 10"            | ИЛИ-НЕ |  |

| 5  | Мультиплексор "8 на 1"            | И-НЕ   |  |

| 6  | Мультиплексор "8 на 1"            | ИЛИ-НЕ |  |

| 7  | Демультиплексор "1 на 8"          | И-НЕ   |  |

| 8  | Демультиплексор "1 на 8"          | ИЛИ-НЕ |  |

| 9  | 5- разрядный мажоритарный элемент | И-НЕ   |  |

| 10 | 5- разрядный мажоритарный элемент | ИЛИ-НЕ |  |

#### Библиографический список

- 1. Алексенко А.Г., Шагурин И.И. Микросхемотехника: Учеб. пособие для вузов. 2-е изд., перераб. и доп. М.: Радио и связь, 1990. С. 156 237.

- 2. Цифровая и вычислительная техника: Учебник для вузов / Э.В. Евреинов, Ю.Т. Бутыльский, И.А. Мамзелев и др.; Под ред. Э.В. Евреинова М.: Радио и связь, 1991. С. 91 147.

- 3. Потемкин И.С. Функциональные узлы цифровой автоматики. М.: Энергоатомиздат, 1988. С. 121 149.

# ЛАБОРАТОРНАЯ РАБОТА № 3 МОДЕЛИРОВАНИЕ ПОСЛЕДОВАТЕЛЬНОСТНЫХ ЦИФРОВЫХ УСТРОЙСТВ

**Цель работы:** обучение методике проектирования последовательностных цифровых устройств, изучение дополнительных возможностей пакета прикладных программ для проектирования ПЛИС фирмы XILINX.

# 1. Подготовка к работе

Перед началом работы требуется изучить теорию, представленную в рекомендуемой литературе.

# 2. Теоретические сведения

Основными типами последовательностных функциональных узлов являются регистры, счетчики и генераторы чисел.

В данной работе рассмотрены счетчики. Счетчиком называется узел, на выходах которого образуется число, соответствующее количеству поступивших на вход импульсов. Основным параметром счетчика является

модуль счета  $K_c$ . — максимальное число импульсов, которое может быть сосчитано счетчиком. После поступления  $K_c$  импульсов счетчик должен возвращаться в исходное состояние. Величина  $K_c$  равна числу устойчивых состояний счетчика. Счетчик, содержащий m разрядов (триггеров), может иметь  $2^m$  устойчивых состояний, поэтому его модуль счета  $K_c \leq 2^m$ . Количество поступивших на счетный вход импульсов представляется на выходе счетчика в виде двоичного числа в том или ином коде: прямом дополнительном, циклическом. Обычно счетчики имеют дополнительные входы установки S, позволяющие предварительно установить на выходе счетчика заданное число, или входы сброса R, сигнал на которых (по переднему или заднему фронту) переводит счетчик в исходное состояние [3]. Частота импульсов на выходе последнего разряда счетчика в  $K_c$  раз меньше, чем частота импульсов, поступающих на вход. Поэтому счетчики используются в качестве делителей частоты, обеспечивающих на выходе в  $K_c$  раз меньшую частоту сигнала, чем на входе.

По типу функционирования различают счетчики суммирующие, вычитающие и реверсивные. Суммирующий счетчик выполняет прямой счет, т. е. при поступлении на вход очередного импульса число на выходе счетчика увеличивается па единицу. Вычитающий счетчик производит обратный счет, т. е. при поступлении счетного импульса число на выходе уменьшается на единицу. Реверсивный счетчик может работать в режимах прямого и обратного счета.

Счетчики широко используются в устройствах управления цифровых систем для подсчета числа выполненных операций, в связной и контрольно-измерительной аппаратуре, для определения числа поступивших сигналов и уменьшения их частоты и др. По структурной организации счетчики делятся на параллельные, последовательные и параллельно-последовательные. Они различаются способами подачи счетных импульсов на входы разрядов.

**Параллельные счетчики**. В счетчиках этого типа счетные импульсы одновременно (параллельно) поступают на синхровходы С триггеров во всех разрядах. Параллельные счетчики обычно строятся на базе T-, JK-, D-триггеров, синхронизируемых фронтом.

Структурное проектирование таких счетчиков выполняется с помощью словарного метода [1]. При увеличении модуля счета, т. е. числа разрядов m, в параллельных счетчиках возрастают количество логических элементов и триггеров, требования к числу их входов, существенно усложняется система межсоединений. Поэтому параллельные счетчики m > 6 - 8 используются редко. Для получения модулей  $K_c > 16$  обычно применяются последовательные или параллельно-последовательные счетчики [3].

Последовательные и параллельно-последовательные счетчики. В счетчиках этого типа счетные импульсы подаются только на вход триггера первого разряда. Для каждого из последующих разрядов сигналы переключения поступают с выхода предыдущих разрядов. В результате происходит последовательное переключение разрядов счетчика.

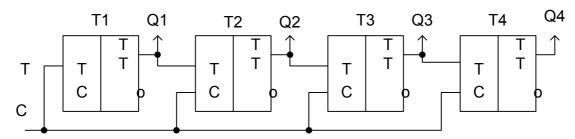

Последовательные счетчики с модулями счета  $K_c$  обычно реализуются последовательным соединением m Т-триггеров, каждый из которых работает как счетчик с  $K_c = 2$ . Структурная схема и временная диаграмма такого суммирующего счетчика с  $K_c = 16$  показаны на рис.1.

Рис.1. Последовательный счетчик на Т - триггерах

Отметим, что данная схема будет работать как вычитающий счетчик, если вход T каждого последующего (k-го) триггера подключить к неинвертирующему выходу  $Q_{k-1}$  предыдущего триггера, а асинхронные входы  $S_d$  использовать для установки какого-либо начального числа. Реверсивный счетчик можно реализовать, включив на счетном входе каждого из триггеров элемент И—ИЛИ—НЕ, выполняющий функцию

$$Tk = \overline{MQk + 1 + \overline{M}Qk - 1} \quad .$$

Для получения модулей счета  $K_c \neq 2^{\rm m}$  в последовательных счетчиках на Т-триггерах требуется включение дополнительных логических элементов. Один из способов реализации таких счетчиков состоит в использовании входов сброса триггеров. Например, декадный счетчик ( $K_c = 10$ ) можно получить из последовательного 4-разрядного счетчика с  $K_c = 16$ , если при поступлении 10-го импульса T = 1, когда установится состояние выходов  $Q_0Q_1Q_2Q_3 = 0101$ , подать на общий и ход сброса сигнал R = 1. Для этого используется управляющая комбинационная схема, выходная функция R которой равна 1 только при  $Q_3 = Q_1 = 1$  и  $Q_0 = Q_2 = 0$ . После минимизации получаем выражение функции

$$R=\overline{\overline{Q}1}+\overline{\overline{Q}3},$$

которое реализуется с помощью элемента ИЛИ — НЕ, подключаемого ко входу R последовательного счетчика.

## Обозначения триггеров в программе:

FDC – D-триггер;

FTC – Т-триггер;

FJKС – JK-триггер;

FJKRSE – JK- триггер с преимущественным сбросом;

FJKSRE – JK-триггер с преимущественной предустановкой.

#### 2. Порядок выполнения работы

- 1. Получить у преподавателя вариант задания согласно номеру бригады (см. таблицу).

- 2. Спроектировать логическую схему последовательностного устройства по методике, изложенной в [1].

- Определить количество ячеек (триггеров), необходимых для реализации заданного устройства.

- Составить таблицу состояний устройства.

- На основании этой таблицы составить карты Карно для функций переходов.

- Минимизировать функции входов триггеров.

- Сформировать логическую схему устройства.

- 3. Сформировать полученную схему с помощью пакета прикладных программ фирмы XILINX, руководствуясь указаниями к лабораторной работе № 1 и используя логические элементы и триггеры из стандартной библиотеки.

- 4. Провести исследование заданной схемы и убедиться в правильности ее работы.

- 5. Представить отчет: распечатка логической схемы и результатов моделирования.

# Библиографический список

- 1. Основы синтеза логических схем: Учеб. пособие / В.Н. Локтюхин. Рязан. гос. радиотехн. академ. Рязань, 2004. 48 с.

- 2. Цифровая и вычислительная техника: Учебник для вузов / Э.В. Евреинов, Ю.Т. Бутыльский, И.А. Мамзелев и др.; Под ред. Э.В. Евреинова М.: Радио и связь, 1991. С. 91 147.

- 4. Потемкин И.С. Функциональные узлы цифровой автоматики. М.: Энергоатомиздат, 1988. С. 121 149.

# Варианты заданий к лабораторной работе № 3

| N₂ | Тип счетчика             | Коэффициент | Тип       |

|----|--------------------------|-------------|-----------|

|    |                          | счета       | триггеров |

| 1  | Параллельный суммирующий | 10          | D         |

| 2  | Параллельный вычитающий  | 11          | D         |

| 3  | Параллельный суммирующий | 11          | T         |

| 4  | Параллельный вычитающий     | 12 | T  |

|----|-----------------------------|----|----|

| 5  | Параллельный суммирующий    | 10 | JK |

| 6  | Параллельный вычитающий     | 11 | JK |

| 7  | Параллельный суммирующий    | 12 | D  |

| 8  | Параллельный вычитающий     | 13 | D  |

| 9  | Параллельный суммирующий    | 14 | T  |

| 10 | Параллельный вычитающий     | 13 | T  |

| 11 | Параллельный суммирующий    | 12 | JK |

| 12 | Последовательный            | 11 | JK |

|    | суммирующий                 |    |    |

| 13 | Последовательный вычитающий | 11 | D  |

| 14 | Последовательный            | 12 | D  |

|    | суммирующий                 |    |    |

| 15 | Последовательный вычитающий | 12 | JK |

#### ЛАБОРАТОРНАЯ РАБОТА № 4

# РАЗРАБОТКА СХЕМЫ ФОРМИРОВАНИЯ ШИРОТНО-ИМПУЛЬСНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ

**Цель работы**: обучение методики проектирования схем формирования широтно-импульсной последовательности.

# 1. Подготовка к работе

Перед началом работы требуется изучить теорию, представленную далее.

# 2. Теоретические сведения

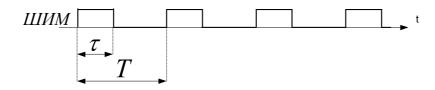

Широтно-импульсная модуляция (ШИМ) характеризуется относительной длительностью (скважностью)  $Q = \tau/T$ , где T — период импульсного сигнала,  $\tau$  — длительность единичного фронта (рис.1).

Рис.1. Модулированный широтно-импульсный сигнал

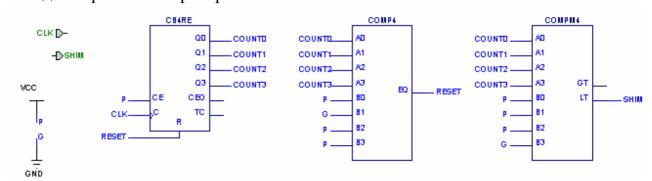

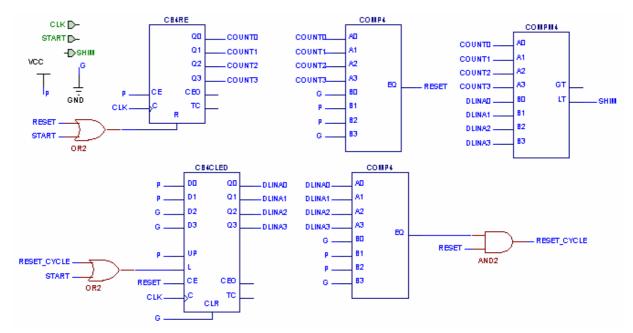

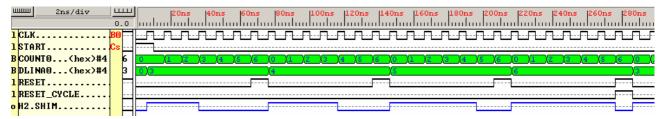

Скважность может быть как одинаковой, так и переменной. Для построения схемы, формирующей ШИМ с постоянной скважностью (рис.2), требуется счетчик и два компаратора. Счетчик, работающий по тактовой частоте clk, формирует длительность периода T, по достижении которого сбрасывается в начальное значение. Сигнал сброса reset формирует первый компаратор. Второй компаратор сравнивает текущее значение count счетчика с величиной  $\tau$  внутри периода T. Выходной сигнал схемы shim снимается с выхода второго компаратора.

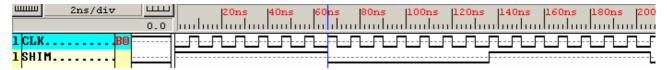

Рис.2. Схема формирования ШИМ с постоянной скважностью Q = 7/14 Временные диаграммы работы схемы, приведенной на рис. 2.2, приведены далее (рис. 2.3):

Рис.3. Результаты моделирования схемы формирования ШИМ с постоянной скважностью Q = 7/14

Схема формирования ШИМ с переменной скважностью (рис.4) состоит из двух счетчиков и трех компараторов. Первый счетчик формирует сигнал count, отсчитывающий период T. Сброс его осуществляется либо по сигналу запуска start, либо по достижении периода T. Сигнал reset вырабатывается первым компаратором как признак окончания периода T. По сигналу reset происходит также приращение скважности на втором счетчике. Выходной сигнал схемы shim снимается с выхода второго компаратора. Третий компаратор вырабатывает признак очередного повторения цикла reset cycle.

Рис. 4. Схема формирования ШИМ с переменной скважностью  $Q = 3/7 \div 6/7$

Временные диаграммы работы схемы, приведенной на рис. 4, приведены далее (рис.5):

Рис. 5. Результаты моделирования схемы формирования ШИМ с переменной скважностью  $Q = 3/14 \div 6/14$

# 3. Порядок выполнения работы

- 3.1. Получить у преподавателя задание согласно номеру бригады (см. таблицу).

- 3.2. Провести синтез счетчика требуемого типа (см. лаб. Работу №3).

- 3.3. Построить схему формирования ШИМ.

- 3.4. Составить отчет.

# Варианты заданий к лабораторной работе № 5

|   | Вид скважности | $Q = \tau / T$ | Тип счетчика | Разрядность |

|---|----------------|----------------|--------------|-------------|

| 1 | Постоянная     | 5/15           | D            | 4           |

| 2 | Постоянная     | 6/11           | Т            | 4           |

| 3 | Постоянная     | 3/13           | D            | 4           |

| 4  | Постоянная | 9/11      | T | 4 |

|----|------------|-----------|---|---|

| 5  | Постоянная | 4/12      | D | 4 |

| 6  | Постоянная | 8/13      | Т | 4 |

| 7  | Постоянная | 11/15     | D | 4 |

| 8  | Постоянная | 4/15      | T | 4 |

| 9  | Переменная | 1/7 - 6/7 | D | 3 |

| 10 | Переменная | 1/7 - 6/7 | T | 3 |

| 11 | Переменная | 2/7 - 5/7 | D | 3 |

| 12 | Переменная | 2/7 - 5/7 | T | 3 |

| 13 | Переменная | 1/7 - 5/7 | D | 3 |

| 14 | Переменная | 1/7 - 5/7 | T | 3 |

| 15 | Переменная | 2/7 - 6/7 | D | 3 |

| 16 | Переменная | 2/7 - 6/7 | Т | 3 |

# **ЛАБОРАТОРНАЯ РАБОТА № 5 РАЗРАБОТКА ДИСПЕТЧЕРА ПАМЯТИ**

**Цель работы**: обучение методике проектирования диспетчера памяти, изучение принципов работы с внешним запоминающим устройством.

## 1. Подготовка к работе

Перед началом работы требуется изучить теорию, представленную далее.

# 2. Теоретические сведения

Диспетчер памяти необходим для обращения к одному модулю памяти от нескольких потребителей (каналов). Диспетчер памяти состоит из двух компонент: контроллера памяти и блока приоритетов.

Контроллер памяти осуществляет:

- 1) выдачу сигналов разрешения записи и чтения на память;

- 2) установку адреса обращения к памяти;

- 3) переключение двунаправленной шины данных в зависимости от вида обращения (записи или чтения);

- 4) прием данных из памяти при чтении.

Блок приоритетов формирует ответ тому каналу, запрос на обращение алгоритму которому следует удовлетворить. По памяти ПО функционирования блоки приоритетов абсолютные делятся на И относительные.

В блоке с абсолютными приоритетами все каналы имеют свой строго определенный приоритет. Это означает, что если имеется запрос по каналу с наивысшим приоритетом, то выполняется именно он. Запрос по каналу с

самым низким приоритетом выполняется только в том случае, если нет запросов ни по одному из других каналов.

В блоке с относительными приоритетами ответ выдается тому каналу, в очереди запросов которого находится наибольшее количество элементов.

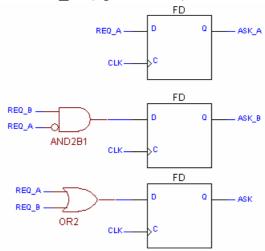

На рис.1 показан двухканальный блок абсолютных приоритетов, где  $req\_a$  — запрос по каналу с высшим приоритетом,  $req\_b$  — запрос по каналу с низшим приоритетом,  $ask\_a$  и  $ask\_b$  — ответы на запросы по каналам, ask — общий ответ. В следующем такте после выставления сигнала ask на контроллер памяти подаются признак чтения/записи  $rd\_wr$  ( $rd\_wr$ =1 при чтении), адрес adr и данные d in (при записи).

Рис.1. Двухканальный блок абсолютных приоритетов

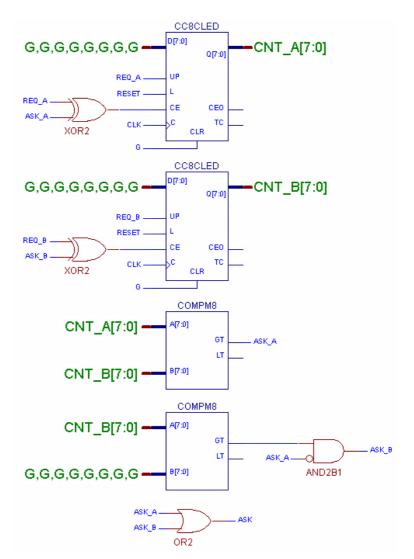

На рис. 2 показан двухканальный блок относительных приоритетов. На схеме имеют место следующие обозначения:  $cnt_a$  — число неотвеченных запросов по каналу a, cnt b — число неотвеченных запросов по каналу b.

Функционирование контроллера памяти зависит от ее типа. Память бывает синхронной и асинхронной.

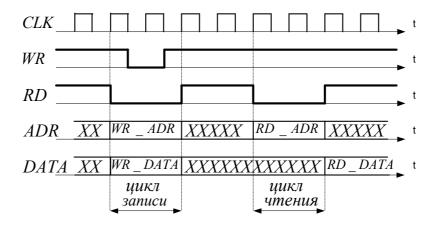

Асинхронная память характеризуется длительностью цикла  $t_{ij}$  обращения к ней. Это время, как правило, составляет 20-30 ns. Особенностью данного типа памяти является то, что между соседними обращениями на запись и чтение должен быть свободный цикл. Временные диаграммы по чтению и записи асинхронной памяти показаны на рис.3.

Для асинхронной памяти максимальная тактовая частота CLK работы схемы выбирается исходя из выражения:  $CLK \le 2/t_{_{ij}}$ . При удовлетворении данного условия цикл обращения по записи или чтению длится 2 такта.

Рис.2. Двухканальный блок относительных приоритетов

Рис. 3. Временные диаграммы циклов чтения и записи асинхронной памяти

Сигналы разрешения записи WR и чтения RD при отсутствии обращения к памяти устанавливаются в "1". При чтении памяти сигнал RD устанавливается в "0" и удерживается в течении времени  $t_{u}$ . При этом на память выставляется адрес  $ADR = RD\_ADR$ . По истечении  $t_{u}$  с памяти снимаются данные  $RD\_DATA$ . При записи в память сигнал RD

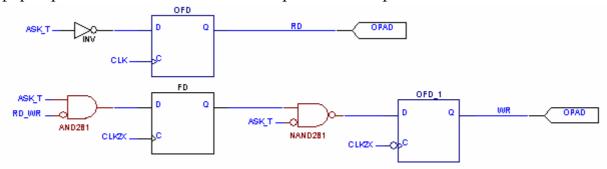

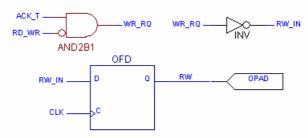

устанавливается в "0". Вместе с этим на память выставляются адрес  $WR\_ADR$  и данные  $WR\_DATA$ . Сигнал WR устанавливается в "0" по истечении времени, равного  $t_{ij}/4$  после начала обращения, и удерживается в данном положении в течении интервала времени, равного  $t_{ij}/2$ . Схема формирования сигналов WR и RD приведена на рис. 1.4.

Рис.4. Установка признаков чтения и записи для асинхронной памяти

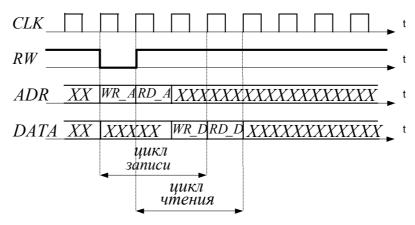

Синхронная память является тактируемой. Цикл обращения к ней составляет 2-3 такта. Длительность обращения здесь определяется периодом тактовой частоты, помноженным на число тактов цикла обращения. Временные диаграммы по чтению и записи синхронной памятью с 2-тактовой задержкой показаны на рис. 1.5.

Рис. 5. Временные диаграммы циклов чтения и записи асинхронной памяти

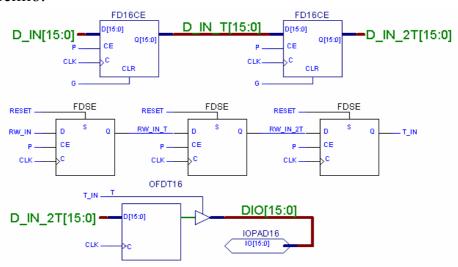

Сигнал признака чтения/записи RW при отсутствии обращения к памяти устанавливается в "1". При чтении сигнал RW устанавливается в "1" и удерживается один такт. При этом на память выставляется адрес  $ADR = RD\_A$ . Спустя 2 такта с памяти снимаются данные  $RD\_D$ . При записи сигнал RW устанавливается в "0". Вместе с этим на память выставляются адрес  $WR\_A$ . Данные  $WR\_D$  подаются на память спустя 2 такта.

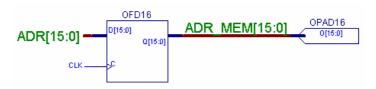

Установка адреса обращения памяти показана на рис.6:

Рис. 6. Установка адреса обращения к синхронной и асинхронной памяти

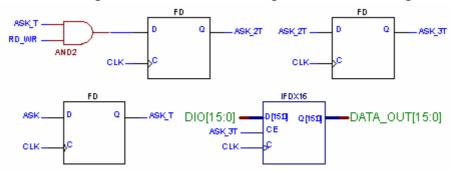

Схема выдачи признака чтения/записи синхронной памяти показана на рис. 7:

Рис. 7. Выдача признака чтения/записи на синхронную память

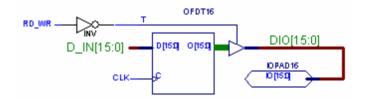

Переключение двунаправленной шины данных в зависимости от вида обращения для синхронной и асинхронной памяти показано на рис.8 и 9 соответственно.

Рис. 8. Переключение двунаправленной шины данных для синхронной памяти

Рис. 9. Переключение двунаправленной шины данных для асинхронной памяти

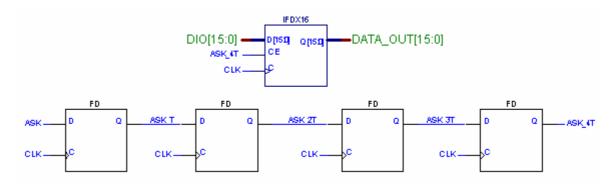

Схемы приема данных из памяти при чтении имеет следующий вид (рис.10 и 11):

Рис. 10. Схема приема данных из синхронной памяти при чтении

Рис.11. Схема приема данных из асинхронной памяти при чтении Результаты использования ресурсов кристалла для одного из вариантов задания приняли вид:

# **Design Summary**

\_\_\_\_\_

Number of errors: 0 Number of warnings: 19

Number of Slices: 7 out of 1,200 1%

Number of Slices containing

unrelated logic: 0 out of 7 0 %

Number of Slice Flip Flops: 8 out of 2,400 1 % Number of 4 input LUTs: 5 out of 2,400 1 % Number of bonded IOBs: 69 out of 166 41 %

IOB Flip Flops: 50

Number of GCLKIOBs: 1 out of 4 25 %

Total equivalent gate count for design: 542 Additional JTAG gate count for IOBs: 3,360

Посмотреть отчет можно в файле *map.mrp* или в окне *Reports* менеджера проектов.

# 3. Порядок выполнения работы

- 3.1. Получить у преподавателя задание согласно номеру бригады (см. таблицу).

- 3.2. Построить блок приоритетов (см. примеры на рис. 1 и 2).

- 3.3. Выбрать тактовую частоту (для асинхронной памяти).

- 3.4. Построить схему установки адреса обращения к памяти.

- 3.5. Построить схему выдачи сигналов разрешения записи и чтения на память.

- 3.6. Построить схему переключения двунаправленной шины данных.

- 3.7. Построить схему приема данных из памяти.

- 3.8. Провести трассировку схемы.

Для этого необходимо в окне *Project Manager* запустить *Implementation*. При запуске разводки необходимо будет задать следующие опции:

*Options→Simulation*=OFF,

$Options \rightarrow Implementation \rightarrow Optimize \ and \ Map \rightarrow Trim \ Unconnected \ Logic = OFF.$

- 3.9. С помощью Tools→Implementation→Floorplanner запустить утилиту Floorplanner и посмотреть размещение проекта в кристалл.

- 3.8. Составить отчет.

# Варианты заданий к лабораторной работе № 5

|    | Типа памяти | Тип приоритетов | Задержка | Количество<br>каналов |

|----|-------------|-----------------|----------|-----------------------|

| 1  | Синхронная  | Абсолютный      | 2 такта  | 3                     |

| 2  | Синхронная  | Абсолютный      | 2 такта  | 4                     |

| 3  | Синхронная  | Абсолютный      | 3 такта  | 3                     |

| 4  | Синхронная  | Абсолютный      | 3 такта  | 4                     |

| 5  | Синхронная  | Относительный   | 2 такта  | 3                     |

| 6  | Синхронная  | Относительный   | 2 такта  | 4                     |

| 7  | Синхронная  | Относительный   | 3 такта  | 3                     |

| 8  | Синхронная  | Относительный   | 3 такта  | 4                     |

| 9  | Асинхронная | Абсолютный      | 20 ns    | 3                     |

| 10 | Асинхронная | Абсолютный      | 20 ns    | 4                     |

| 11 | Асинхронная | Абсолютный      | 30 ns    | 3                     |

| 12 | Асинхронная | Абсолютный      | 30 ns    | 4                     |

| 13 | Асинхронная | Относительный   | 20 ns    | 3                     |

| 14 | Асинхронная | Относительный   | 20 ns    | 4                     |

| 15 | Асинхронная | Относительный   | 30 ns    | 3                     |

# ОПИСАНИЕ ИНТЕРФЕЙСА СХЕМОТЕХНИЧЕСКОГО РЕДАКТОРА

#### 1.1. Определение схемы

Редактор обычно используется для создания изображения электрической схемы, которое содержит используемые компоненты и их соединения.

Схемотехническое изображение может быть использовано в твердой копии для документации или сборки схемы.

#### 1.2. Физические и логические соединения

Физическое соединение - это графическая линия (называемая проводом), проводимая на схеме между двумя или более выводами.

Логическое соединение делается между двумя или более выводами без изображения провода. Это делается присвоением идентичных имен двум или более проводникам подсоединенными к выводам устройства.

#### 1.3. Интерфейс схемотехнического редактора

Операции редактора управляются активацией иконок или кнопок на вертикальных или функциональных горизонтальных панелях.

# 1.3.1. Управление схемами проектов

Иконки, предназначенные для манипуляций со схемами проектов (*Project Management Icons*):

- Новая схема (New Schematic) запускает новую схему.

- Открыть схему (*Open a Schematic*) открывает одну из существующих схем.

- Сохранить (Save) позволяет сохранить текущие схемные проекты. Иконка активна только в случае, если в схеме были изменения после того, как она последний раз сохранена. В противном случае она останется серой или неактивной.

- Проекты (*Projects*) отображает экран *Project Manager*.

- Печатать схему (*Print a Schematic*) запускает типовую операцию печати *Windows*.

#### 1.3.2. Операции исключения и наклейки

Иконки операций исключения, копирования и наклейки требуют установки редактора в режим *Select* нажатием иконки *Select and Drug*.

• Вырезать (*Cut*) - позволяет «забрать» выбранный элемент схемы в «карман». Сначала активизируйте режим *Select* нажатием на иконку *Select and Drug*. Далее переместите прямоугольник к выбранным элементам или выберите их нажатием клавиши *Shift* на каждом элементе. Нажатием на *Cut* удаляет выделенные элементы из схемы и помещает их в «карман». Все

провода, полностью остающиеся в удаляемой области, также копируются в «карман».

- Копировать (*Copy*) позволяет копировать фрагмент схемы в «карман». Выберите копируемые элементы и нажмите на *Copy*.

- Клеить (*Paste*) помещает содержимое «кармана» в выбранную позицию экрана. Первая активация *Paste* отображает отмеченное рамкой содержимое «кармана». Второе нажатие *Paste* помещает это содержимое в выбранную позицию.

#### 1.3.3. Операции масштабирования

Группа иконок Zoom Operations изменяет масштаб выводимых на экран схем.

- Две кнопки масштаб (*Zoom*). Значение плюс (+) представляет опцию «Увеличить изображение» (*Zoom in*), а значок минус (-) опцию «Уменьшить изображение» (*Zoom out*).

- Область масштабирования (*Zoom Area*) обеспечивает выбор фрагмента схемы, который будет отображен на полном экране. Первое нажатие *Zoom Area* активизирует курсор выбора. Поместите курсор в противоположный угол фрагмента. По освобождении мыши выбранная область расширится на весь экран.

#### 1.3.4. Операции редактирования

Иконки управления операциями редактирования:

- Отменить (*Undo*)- отменяет последнее схемное изменение и восстанавливает состояние схемы до него.

- Назначения (*Properties*) -позволяет изменять атрибуты проводов и обозначение элементов.

- Присоединить элемент (*Connect Symbol*) соединяет выводы элементов с перекрытием с обозначениями конца провода (круг или квадрат с крестиком). Эти операции используются для замены деталей или присоединения проводов.

- Отсоединить элемент (Disconnect Symbol) отсоединяет все провода от выбранного элемента и размещает обозначения концов отсоединенных проводов.

- Конец (*End*) используется для разрыва проводов и шин в текущей позиции экрана. Провода могут разрываться введением обозначения их концов.

- М Отмена (Cancel) прерывает вычеркивание проводов и шин.

#### 1.3.5. Операции ввода схемы

Иконки операций ввода схемы размещаются на левой стороне экрана. Однако они могут быть перемещены в другую позицию экрана.

- Элементная панель инструментов (*Symbol Toolbox*) активизирует средства с обозначением устройства. Панель инструментов (*toolbox*) включает также иконки для выбора желаемых типов обозначений и позволяет поиск для выбранной детали или типов деталей.

- Рисовать провода (*Draw Wires*) активизирует режим вычерчивания проводов. Нажатие на контакт начинает провод. Нажатие на другой контакт автоматически рисует провод. Двойное нажатие на пустом месте начинает провод с обозначением конца провода.

- Рисовать шины ( $Draw\ Buses$ ) позволяет рисовать шины нажатием в любой позиции экрана. Для окончания шины нажмите правую клавишу мыши или активируйте иконку  $O\kappa$ .

- Рисовать шинные контакты (*Draw Bus Tops*) запускает вычерчивание соединений между шинами и контактами ответвление шин. Нажатие на шину, а затем на обозначения контактов автоматически соединит эти контакты с шинами и ответвлениями.

- Добавить имя соединения или провода (Add Net or Bus Name) используется для наименования проводов и шин. Нажатие на провод или шину в режиме Select окрасит выбранный элемент в красный цвет. Активизация иконки Add Net or Bus Name отобразит окно для наименования выбранных элементов.

- Элемент питания (*Power Symbol*) позволяет прямое размещение обозначений питания на схеме. Иконка активна только, если также активна иконка *Draw Wires*.

- Терминал ввода/вывода (*I/O Terminal*) позволяет наименование клемм ввода/вывода и задание их направления. Предварительно активизируется *Draw Wires*.

- Панель инструментов для графики (*Graphics Toolbox*) позволяет вычерчивать графические элементы. Все элементы, рисуемые в этом режиме, не имеют электрических свойств. Этот режим используется для неэлектрических рисунков, для добавления информации, которую не нужно сохранять в электрической базе данных.

#### 1.3.6. Общие операции

Выбор и перемещение икон - наиболее частая операция для выбора объектов на схеме и их обработки. Опция *Select* установлена автоматически для нескольких операций редактора.

**Координаты**. Строка статуса в нижнем левом углу отображает координаты курсора при его движении по схеме. Значение координат выдается в дюймах, миллиметрах или ссылках на зону. Выбор одного из этих типов - опция  $Page\ Setup$  в меню File.

**Масштаб** (*Ruler*). Отображение масштаба управляется опцией *View: Ruler*. Отображается слева (вертикальный) и наверху (горизонтальный) в каждом схемном окне.

Прямоугольники скроллинга размещены в правом нижнем углу каждого схемного окна. Операция позволяет плавное перемещение (скроллинг) по схеме в горизонтальном и вертикальном направлениях.

Георгиевич, Заведующий кафедрой МНЭЛ